# A PORTABLE RUNTIME INTERFACE FOR MULTI-LEVEL MEMORY HIERARCHIES

A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Michael C. Houston March 2008

© Copyright by Michael C. Houston 2008 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Patrick M. Hanrahan (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Alex Aiken

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

William J. Dally

Approved for the University Committee on Graduate Studies.

### Abstract

The efficient use of a machine's memory system and parallel processing resources has become one of the most important challenges in program optimization. Moreover, efficient use of the memory hierarchy is increasingly important because of the power cost of data transfers through the system. Architecture trends are leading to large scale parallelism using simpler cores and progressively deeper and complex memory hierarchies. These new architecture designs have improved power characteristics and can offer large increases in performance, but traditional programming techniques are inadequate for these architectures.

In this dissertation, we explore a programming language and runtime system for making efficient use of the memory hierarchy and parallel processing resources. This dissertation provides an overview of Sequoia, a programming language we have developed at Stanford to facilitate the development of memory hierarchy aware parallel programs that remain portable across modern machines featuring different memory hierarchy configurations. Sequoia abstractly exposes hierarchical memory in the programming model and provides language mechanisms to describe communication vertically through the machine and to localize computation to particular memory locations within it.

This dissertation presents a platform independent runtime interface for moving data and computation through parallel machines with multi-level memory hierarchies. We show that

this interface can be used as a compiler target for the Sequoia language and compiler, and can be implemented easily and efficiently on a variety of platforms. The interface design allows us to compose multiple runtimes, achieving portability across machines with multiple memory levels. We demonstrate portability of Sequoia programs across machines with two memory levels with runtime implementations for multi-core/SMP machines, the STI Cell Broadband Engine, a distributed memory cluster, and disk systems. We also demonstrate portability across machines with multiple memory levels by composing runtimes and running on a cluster of SMP nodes, out-of-core algorithms on a Sony Playstation 3 pulling data from disk, and a cluster of Sony Playstation 3's. All of this is done without any source level modifications to the Sequoia program. With this uniform interface, we achieve good performance for our applications and maximize bandwidth and computational resources on these system configurations.

### Acknowledgments

I first need to thank all of my research collaborators, especially those on working with me on the Sequoia project: Ji-Young Park, Manman Ren, Tim Knight, Kayvon Fatahalian, Mattan Erez, and Daniel Horn. I largely attribute the success of the project to all the hard work and long nights required to get all the code written and papers out. Without Kayvon, who lead the language development, and Tim Knight, who lead the compiler work, we never would have been able to get to level where the runtime work was viable. For the last year, Ji-Young and Manman have really been the folks doing a lot of heavy lifting to get all the compiler infrastructure converted over to the runtime system and help get all the applications optimized and tested.

I'd also like to thank Pat Hanrahan for taking a risk and funding me as a Masters student, and then supporting me for entrance into the Ph.D program. Working with Pat has taught me a great deal about doing research and standing up for my ideas. Although my research interests in the end diverged from Pat's area of interest, he was supportive of my pursuits and helped me engage with other groups.

Alex Aiken has gone above and beyond for me and the rest of the people working in the Sequoia project. Although we were not his students, he would meet with us every week, if not more, to help us codify the research goals and directions for the Sequoia project and force us to really work through the issues and to set and make deadlines. Alex was also deeply involved in all of the Sequoia publications, even editing papers and my dissertation while on his "year off" traveling around the world.

I have had many influences while at Stanford which contributed to my success. My first year was spent under the wing of Greg Humphreys, while although an interesting character and often a distraction, really taught me how to handle working on large systems projects and survive with humor. Working with Ian Buck on the Brook project and then subsequent work on GPGPU gave me perhaps more than my fair share of visibility, which in turn helped to secure later funding, fellowships, and solid job offers. Ian was of great help reassuring me that I really would finish and get everyone to read and sign my dissertation. Jeremy Sugerman often served as the voice of pragmatism, and sometimes sanity; he approaches most things with sarcasm and humor making sure things arent put up on a pedestal, and is quick to call people on being vague or fluffy when a deeper explanation is really required. Daniel Horn is an amazing hacker who was the first real user of the Sequoia system and worked with me on many papers and system projects. Kayvon Fatahalian is an amazing researcher who has made me really think carefully through my research and served as my primary sounding board for all my various research ideas and proposed solutions.

I have had a variety of funding sources throughout my career including DOE, ASC, LLNL, ATI, IBM, and Intel. Specifically, I'd like to thank Randy Frank, Sean Ahern, and Sheila Vaidya from LLNL and Allen McPherson and Pat McCormick from LANL for supporting much of my research as well as interacting closely with us on projects. I'd also like to thank Bob Drebin, Eric Demers, and Raja Koduri from ATI/AMD for letting me come in to ATI for internships and consulting and be disruptive, in a good way. I was able to learn a tremendous about GPU architectures, memory systems, working with large teams, and how to hold my ground when I think I'm on the right path. IBM was gracious in providing us with early access to IBM Cell blade systems to start the Sequoia project, a large reason

for the early success of the project. I was honored to receive a graduate fellowship from Intel for my final two years of research. This fellowship allowed me to concentrate purely on the Sequoia project as well as interact with some amazing people at Intel.

I would like to thank my committee members, Vijay Pande and Mendel Rosenblum, for providing feedback on my research and willingness to sit on my committee. Special thanks to my readers, Pat Hanrahan, Alex Aiken, and Bill Dally for helping me get everything into a coherent text and present the reams of numbers in a reasonable way. Bill got back to me on my dissertation much faster than expected and really helped to clean up some of the reasoning.

Being at Stanford has been an amazing experience, and I'm glad I took the risk to come here. The quality of the students and faculty is just simply amazing, and I was constantly challenged as well as humbled. It's amazing when someone outside of your area can quickly understand your research, and poke holes in your assumptions, and help you to better mold how you present and talk about things. Being in the graphics lab is a valuable, if not intimidating, experience. I think our lab is incredibly hard on speakers, but the feedback is very constructive and helps you to develop a thick skin, a requirement for both academia and industry, and quickly improve how you present your research. I was extremely hard on infrastructure and resources for my research, so I'd especially like to thank Ada Glucksman, Heather Gentner, John Gerth, Joe Little, and Charlie Orgish for being there when I needed them for help.

Last, but not least, I'd like to thank my family. My parents have been very supportive through my education, even during the dark times when I as really struggling, and have been willing to put themselves on the line for me when it has come to my education. Id like to thank my sister Janice for saving my life more than once and putting up with me when I used to really pester her. I'd also really like to thank my wife's family, James, Ruth and

Aaron for welcoming me into their home during my time at Stanford. I'd like to especially thank my mother-in-law for preparing so many meals for me when I have been busy. And most importantly, I need to thank my loving wife, Tina, who has been there for me during the best and worst of times. She understood during paper crunches when I'd disappear for weeks and when I was not in the best of moods. She was even patient when forced to read multiple drafts of my papers and this dissertation. I could not have gotten through everything without her support and love.

Thank you all!

For all those who helped me along the way, this would not have been possible without you...

# Contents

| Al | bstract         |         |                             |    |

|----|-----------------|---------|-----------------------------|----|

| Ac | Acknowledgments |         |                             | vi |

| 1  | Intr            | oductio | n                           | 1  |

|    | 1.1             | Thesis  | Contributions               | 5  |

|    | 1.2             | Outlin  | e                           | 6  |

| 2  | Bac             | kgroun  | d                           | 7  |

|    | 2.1             | Archit  | ecture Trends               | 7  |

|    |                 | 2.1.1   | Memory Systems              | 7  |

|    |                 | 2.1.2   | From Sequential to Parallel | 10 |

|    | 2.2             | Progra  | mming Systems               | 12 |

|    |                 | 2.2.1   | Programming Models          | 13 |

|    |                 | 2.2.2   | Programming Languages       | 18 |

|    |                 | 2.2.3   | Runtime Systems and APIs    | 22 |

| 3  | Abs             | tract M | achine Model                | 25 |

|    | 3.1             | Memo    | ry Hierarchy Model          | 28 |

|    | 3.2             | Space   | Limited Procedures          | 30 |

|   | 3.3  | The Sequoia Model                           | 33 |

|---|------|---------------------------------------------|----|

| 4 | Sequ | uoia                                        | 37 |

|   | 4.1  | Hierarchical Memory                         | 37 |

|   | 4.2  | Sequoia Language                            | 39 |

|   |      | 4.2.1 Explicit Communication And Locality   | 40 |

|   |      | 4.2.2 Isolation and Parallelism             | 42 |

|   |      | 4.2.3 Task Decomposition                    | 43 |

|   |      | 4.2.4 Task Variants                         | 44 |

|   |      | 4.2.5 Task Parameterization                 | 45 |

|   | 4.3  | Sequoia Compiler                            | 47 |

|   | 4.4  | Specialization and Tuning                   | 49 |

|   | 4.5  | Sequoia System                              | 51 |

| 5 | Port | able Runtime System                         | 54 |

|   | 5.1  | Runtime Interface                           | 54 |

|   |      | 5.1.1 Top Interface                         | 56 |

|   |      | 5.1.2 Bottom Interface                      | 59 |

|   | 5.2  | Runtime Implementations                     | 60 |

|   |      | 5.2.1 SMP                                   | 60 |

|   |      | 5.2.2 Cluster Runtime                       | 62 |

|   |      | 5.2.3 Cell                                  | 64 |

|   |      | 5.2.4 Disk                                  | 66 |

|   | 5.3  | Multi-Level Machines With Composed Runtimes | 67 |

| 6 | Eval | luation                                     | 70 |

|   | 6.1  | Two-level Portability                       | 71 |

|   | 6.2  | Multi-level Portability                     | 82 |

|   |      |                                             |    |

|     | 6.3              | Runtime Overheads       | 86  |

|-----|------------------|-------------------------|-----|

| 7   | Disc             | ussion                  | 90  |

|     | 7.1              | Machine Abstraction     | 90  |

|     | 7.2              | Portable Runtime System | 91  |

|     | 7.3              | Sequoia                 | 93  |

|     | 7.4              | Future Work             | 95  |

| 8   | Con              | clusion                 | 98  |

|     | 8.1              | Thesis Summary          | 99  |

|     | 8.2              | Observations            | 100 |

|     | 8.3              | Last Words              | 103 |

| Bil | Bibliography 104 |                         |     |

# **List of Tables**

| 4.1 | Sequoia mapping and blocking primitives                                        | 53 |

|-----|--------------------------------------------------------------------------------|----|

| 6.1 | Our application suite                                                          | 71 |

| 6.2 | Dataset sizes used for each application for each configuration                 | 72 |

| 6.3 | Two-level Portability - Application performance (GFLOPS) on a 2.4 GHz          |    |

|     | P4 Xeon (Baseline), 8-way 2.6 6GHz Xeons (SMP), with arrays on a single        |    |

|     | parallel ATA drive (Disk), a cluster of 16 2.4 GHz P4 Xeons connected with     |    |

|     | Infiniband (Cluster), a 3.2 GHz Cell processor with 8 SPEs (Cell), and a       |    |

|     | Sony Playstation 3 with a 3.2 GHz Cell processor and 6 available SPEs          | 73 |

| 6.4 | Multi-level Portability - Application performance (GFLOPS) on four 2-          |    |

|     | way, 3.16 GHz Intel Pentium 4 Xeons connected via GigE (Cluster of             |    |

|     | SMPs), a Sony Playstation 3 bringing data from disk (Disk + PS3), and          |    |

|     | two PS3's connected via GigE (Cluster of PS3s)                                 | 83 |

| 6.5 | Overhead time in microseconds for the performance critical code paths.         |    |

|     | For the cluster runtimes, we include results for a transfer that involves data |    |

|     | that is owned by the node (local) as well as data owned by a remote node       |    |

|     | (remote)                                                                       | 86 |

# **List of Figures**

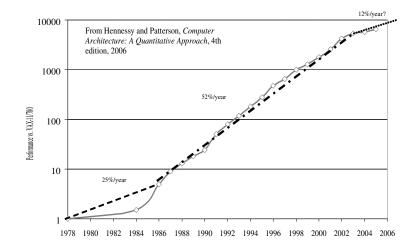

| 2.1 | Single threaded scaling performance has come to an end                        | 10 |

|-----|-------------------------------------------------------------------------------|----|

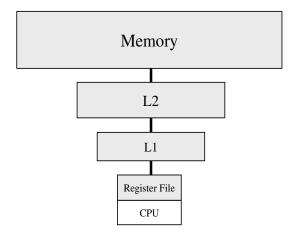

| 3.1 | Intel Pentium4 Uniform Memory Hierarchy example                               | 27 |

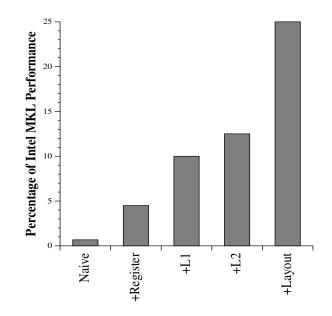

| 3.2 | Optimizing matrix multiply for the memory hierarchy. Starting from a          |    |

|     | naive implementation, we can progressive add more optimizations and get       |    |

|     | to within 1/4 of the performance of the highly tuned MKL library with only    |    |

|     | memory system optimizations.                                                  | 27 |

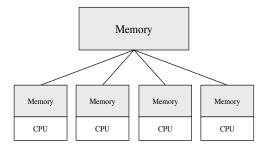

| 3.3 | Two level example of a Parallel Memory Hierarchy                              | 30 |

| 3.4 | Three level example of a Parallel Memory Hierarchy                            | 31 |

| 3.5 | A Cell workstation (left) is modeled as a tree containing nodes correspond-   |    |

|     | ing to main system memory and each of the processor's software-managed        |    |

|     | local stores. A representation of a dual-CPU workstation is shown at right    | 31 |

| 3.6 | Two level example of our abstraction. Each tree node is comprised of a con-   |    |

|     | trol processor and a memory. Interior control processors, denoted with a      |    |

|     | dashed line, can only operate to move data and transfer control to children.  |    |

|     | Leaf control processors are also responsible for executing user defined pro-  |    |

|     | cedures                                                                       | 34 |

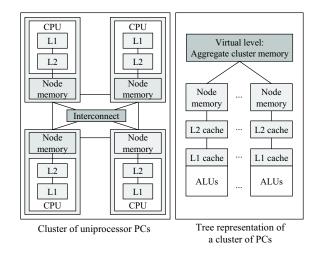

| 3.7 | The point-to-point links connecting PCs in a cluster are modeled as a virtual |    |

|     | node in the tree representation of the machine                                | 35 |

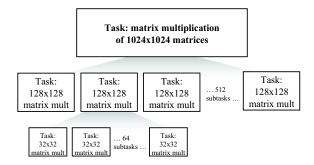

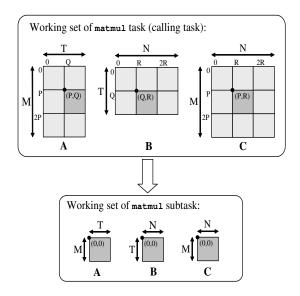

| 4.1  | Multiplication of 1024x1024 matrices structured as a hierarchy of indepen-         |    |

|------|------------------------------------------------------------------------------------|----|

|      | dent tasks performing smaller multiplications                                      | 37 |

| 4.2  | Dense matrix multiplication in Sequoia. matmul::inner and matmul::leaf             |    |

|      | are variants of the matmul task                                                    | 40 |

| 4.3  | The matmul::inner variant calls subtasks that perform submatrix multi-             |    |

|      | plications. Blocks of the matrices $A$ , $B$ , and $C$ are passed as arguments to  |    |

|      | these subtasks and appear as matrices in the address space of a subtask. $\ . \ .$ | 42 |

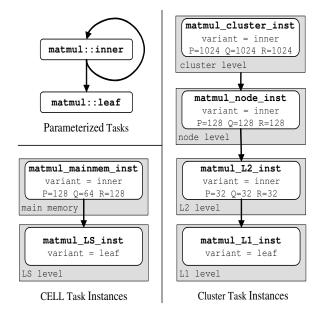

| 4.4  | The call graph for the parameterized matmul task is shown at top left. Spe-        |    |

|      | cialization to Cell or to our cluster machine generates instances of the task      |    |

|      | shown at bottom left and at right                                                  | 45 |

| 4.5  | Specification for mapping the matmul task to a Cell machine (left) and a           |    |

|      | cluster machine (right)                                                            | 49 |

| 4.6  | A tuned version of the cluster mapping specification from Figure 4.5. The          |    |

|      | cluster instance now distributes its working set across the cluster and uti-       |    |

|      | lizes software-pipelining to hide communication latency.                           | 51 |

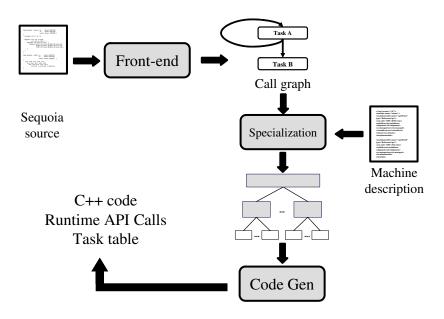

| 4.7  | Sequoia system overview                                                            | 52 |

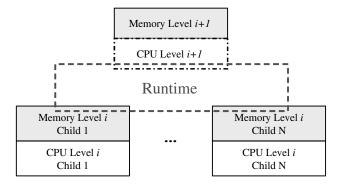

| 5.1  | A runtime straddles two memory levels.                                             | 56 |

| 5.2  | The runtime API Top Interface                                                      | 57 |

| 5.3  | The runtime API Bottom Interface                                                   | 58 |

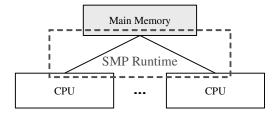

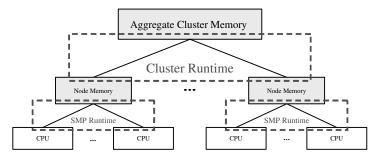

| 5.4  | Graphical representation of the SMP runtime                                        | 61 |

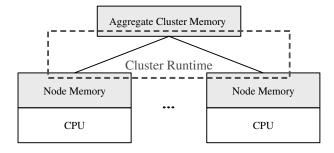

| 5.5  | Graphical representation of the cluster runtime                                    | 62 |

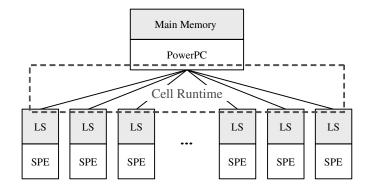

| 5.6  | Graphical representation of the Cell runtime                                       | 65 |

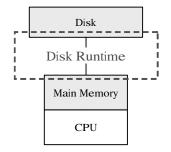

| 5.7  | Graphical representation of the Disk runtime                                       | 66 |

| 5.8  | Hierarchical representation of the composed Disk and PS3 runtimes                  | 67 |

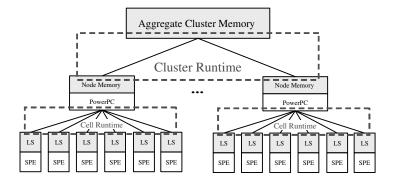

| 5.9  | Hierarchical representation of the composed Cluster and PS3 runtimes               | 68 |

| 5.10 | Hierarchical representation of the composed Cluster and SMP runtimes               | 68 |

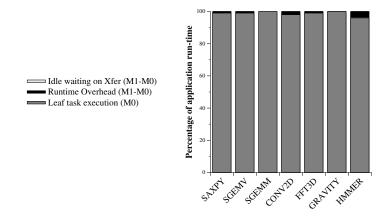

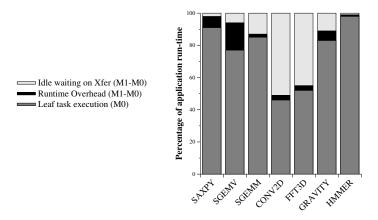

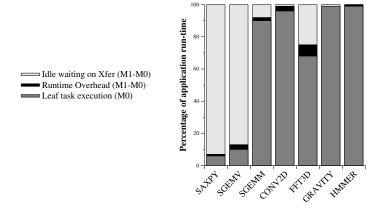

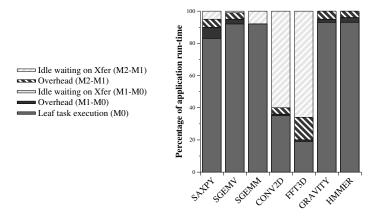

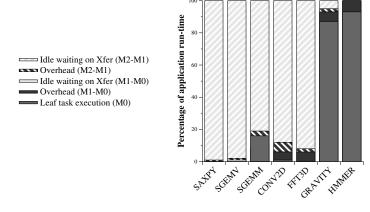

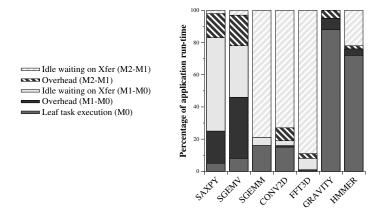

| 6.1  | Execution time breakdown for each benchmark when running on the SMP                      |    |

|------|------------------------------------------------------------------------------------------|----|

|      | runtime                                                                                  | 73 |

| 6.2  | Execution time breakdown for each benchmark when running on the Disk                     |    |

|      | runtime                                                                                  | 73 |

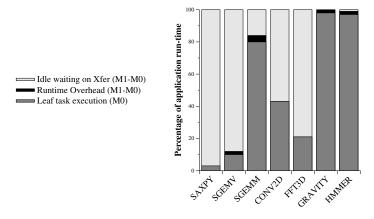

| 6.3  | Execution time breakdown for each benchmark when running on the Clus-                    |    |

|      | ter runtime                                                                              | 74 |

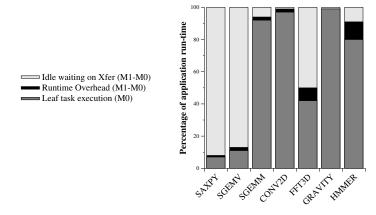

| 6.4  | Execution time breakdown for each benchmark when running with the Cell                   |    |

|      | runtime on the IBM QS20 (single Cell)                                                    | 74 |

| 6.5  | Execution time breakdown for each benchmark when running with the Cell                   |    |

|      | runtime on the Sony Playstation 3                                                        | 74 |

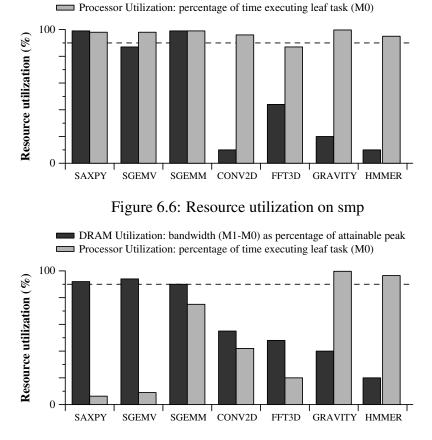

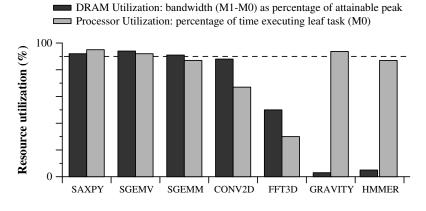

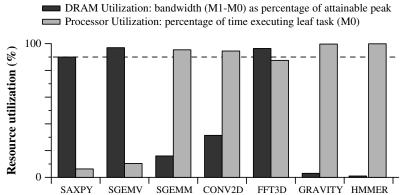

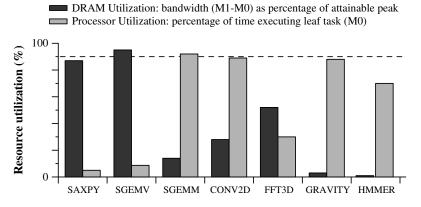

| 6.6  | Resource utilization on smp                                                              | 76 |

| 6.7  | Resource utilization on disk                                                             | 76 |

| 6.8  | Resource utilization on cluster                                                          | 77 |

| 6.9  | Resource utilization on Cell                                                             | 77 |

| 6.10 | Resource utilization on Sony Playstation 3                                               | 77 |

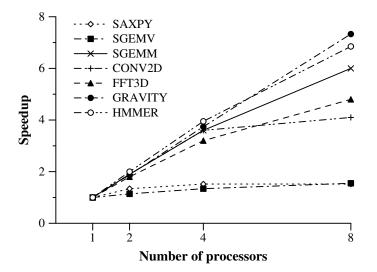

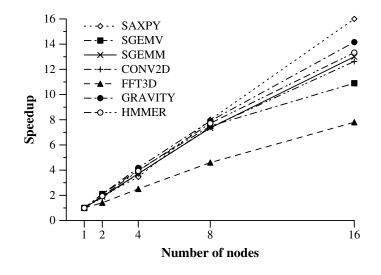

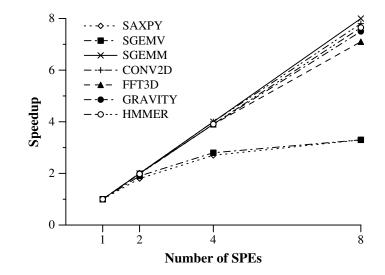

| 6.11 | SMP application scaling                                                                  | 78 |

| 6.12 | Cluster application scaling                                                              | 79 |

| 6.13 | Cell application scaling                                                                 | 79 |

| 6.14 | Execution time breakdown for each benchmark when running on a Cluster                    |    |

|      | of SMPs                                                                                  | 84 |

| 6.15 | Execution time breakdown for each benchmark when running on a Disk+Sony                  |    |

|      | Playstation 3                                                                            | 84 |

| 6.16 | Execution time breakdown for each benchmark when running on a Cluster                    |    |

|      | of Sony Playstation 3's                                                                  | 84 |

|      | Execution time breakdown for each benchmark when running on a Disk+Song<br>Playstation 3 | у  |

## Chapter 1

## Introduction

Current programming languages and runtime systems do not provide the mechanisms necessary to efficiently manage data movement through the memory hierarchy or efficiently manage the parallel computational resources available in the machine. Moreover, previous research has a limited degree of portability across different architectures because of builtin assumptions about the underlying hardware capabilities. Sequoia has been designed to allow efficient use of the memory system and parallel computational resources while providing portability across different machine types and efficient control of complex memory hierarchies.

Most parallel programs today are written using a *two-level* memory model, in which the machine architecture, regardless of how it is physically constructed, is abstracted as a set of sequential processors executing in parallel. Consistent with many parallel programming languages, we refer to the two memory levels as *local* (local to a particular processor) and *global* (the aggregate of all local memories). Communication between the global and local levels is handled either by explicit message passing (as with MPI [MPIF, 1994]) or by language-level distinctions between local and global references (as in UPC [Carlson et al.,

1999] and Titanium [Yelick et al., 1998]). Using a two-level abstraction to program a *multi-level* system, a configuration with more than one level of communication, obscures details of the machine that may be critical to performance. On the other hand, adding support outside of the programming model for moving computation and data between additional levels leads to a multiplicity of mechanisms for essentially the same functionality (e.g., the ad hoc or missing support for out-of-core programming in most two-level systems). It is our thesis that programming abstractions, compilers, and runtimes directly supporting multi-level machines are needed.

This work is based on the belief that three trends in machine architecture will continue for the foreseeable future. First, future machines will continue to increase the depth of the memory hierarchy, making direct programming model support for more than two-level systems important. Second, partly as a result of the increasing number of memory levels, the variety of communication protocols for moving data between memory levels will also continue to increase, making a uniform communication API desirable both to manage the complexity and improve the portability of applications. Lastly, architectures requiring explicit application control over the memory system, often through explicit memory transfers, will become more common. A current extreme example of this kind of machine is LANL's proposed Roadrunner machine, which combines disk, cluster, SMP, and the explicit memory control required by the Cell processor [LANL, 2008].

In this thesis, we present an API and runtime system that virtualizes memory systems, giving a program the same interface to data and computation whether the memory level is a distributed memory, a shared memory multiprocessor (SMP), a single processor with local memory, or disk, among other possibilities. Furthermore, this API is composable, meaning that a runtime for a new multi-level machine can be easily constructed by composing the runtimes for each of its individual levels.

The primary benefit of this approach is a substantial improvement in portability and ease of maintenance of a high performance application for multiple platforms. Consider, for example, a hypothetical application that is first implemented on a distributed memory cluster. Typically, such a program relies on MPI for data transfer and control of execution. Tuning the same application for an SMP either requires redesign or reliance on a good shared memory MPI implementation. Unfortunately, in most cases the data transfers required on the cluster for correctness are not required on a shared memory system and may limit achievable performance. Moving the application to a cluster of SMPs could use a MPI process per processor, which relies on a MPI implementation with recognition of which processes are running on the same node and which are on other nodes to orchestrate efficient communication. Another option is to use MPI between nodes and Pthreads or OpenMP compiled code within a node, thus mixing programming models and mechanisms for communication and execution. Another separate challenge is supporting out-of-core applications which need to access data from disk, which adds yet another interface and set of mechanisms that need to be managed by the programmer. As a further complication, processors that require explicit memory management, such as the STI Cell Broadband Engine, present yet another interface that is not easily abstracted with traditional programming techniques.

Dealing with mixed mode parallel programming and the multiplicity of mechanisms and abstractions makes programming for multi-level machines a daunting task. Moreover, as bandwidth varies through the machine, orchestrating data movement and overlapping communication and computation become difficult.

The parallel memory hierarchy (PMH) programming model provides an abstraction of multiple memory levels [Alpern et al., 1993]. The PMH model abstracts parallel machines as trees of memories with slower memories toward the top near the root, faster memories toward the bottom, and with CPUs at the leaves. The Sequoia project has created a full language, compiler, runtime system, and a set of applications based on the PMH model [Fatahalian et al., 2006; Knight et al., 2007; Houston et al., 2008]. The basic programming construct in Sequoia is a *task*, which is a function call that executes entirely in one level of the memory hierarchy, except for any *subtasks* that task invokes. Subtasks may execute in lower memory levels of the system and recursively invoke additional subtasks at even lower levels. All task arguments, including arrays, are passed by value-result (i.e., copy-in, copy-out semantics). Thus, a call from a task to a subtask represents bulk communication, and all communication in Sequoia is expressed via task calls to lower levels of the machine. The programmer decomposes a problem into a tree of tasks, which are subsequently mapped onto a particular machine by a compiler using a separate *mapping* dictating which tasks are to be run at which particular machine levels.

Although our early Sequoia work demonstrated applications running on IBM Cell blades and a cluster of PCs, it did not show portability to multi-level memory hierarchies. More importantly this earlier work also relied on a custom compiler back-end for Cell and a complex and advanced runtime for a cluster of PCs which managed all execution and data movement in the machine through a JIT mechanism. The difficulty with this approach is that every new architecture requires a monolithic, custom backend and/or a complex runtime system.

The Sequoia compiler, along with the bulk optimizations and custom backend used for Cell, is described by Knight et al. [Knight et al., 2007]; the Sequoia language, programming model, and cluster runtime system is described by Fatahalian et al. [Fatahalian et al., 2006]. In this dissertation, we build on the previous PMH and Sequoia work, but we take the approach of defining an abstract runtime interface as the target for the Sequoia compiler and provide separate runtime implementations for each distinct kind of memory in a system. As discussed above, our approach is to define a single interface that all memory levels support.

Since these interfaces are composable, adding support for a new architecture only requires assembling an individual runtime for each adjacent memory level pair of the architecture rather than reimplementing the entire compiler backend.

### **1.1 Thesis Contributions**

This dissertation explores the design and development of an abstract machine model and runtime system for efficiently programming parallel machines with multi-level memory hierarchies. We make several contributions in the areas of computer systems, parallel programming, machine abstractions, and portable runtime systems outlined below. Our approach is to define a single interface that provides one abstraction for communication and control between multiple levels in a memory hierarchy. Since these interfaces are composable, adding support for a new architecture only requires assembling an individual runtime for each adjacent memory level pair of the architecture rather than reimplementing a specialized program for each machine or a custom compiler backend.

- Abstract machine model for parallel machines We present a uniform scheme for explicitly describing memory hierarchies. This abstraction captures common traits important for performance on memory hierarchies. We formalize previous theoretical models and show how the proposed abstraction can be composed to allow for the execution on machines with multiple levels of memory hierarchy.

- **Portable runtime API** We discuss the development and implementation of a runtime API that can be mapped to many system configurations. This interface allows a compiler to optimize and generate code for a variety of machines without knowledge of the specific bulk communication and execution mechanisms required by the machine

configuration. We explore the abstraction by evaluating the efficiency of implementations on several common parallel system configurations.

### **1.2** Outline

The centerpieces of this thesis are the abstract machine model and runtime interface for memory hierarchies, enabling Sequoia to run on multiple architectures, its implementation on various architectures, and the analysis of the portability and efficiency of the abstraction on multiple platforms, including the cost of mapping the abstraction to each platform. The Sequoia language and complete system are discussed, but the focus of the discussion is on the features of the language and the design decisions made along the way to preserve portability and maintain performance on our platforms. Some of these decisions directly impact the types of applications that can be written easily in Sequoia and executed efficiently on our runtime systems. These unintended consequences are discussed in the discussion (Chapter 7).

## Chapter 2

### Background

### 2.1 Architecture Trends

#### 2.1.1 Memory Systems

In modern architectures, the throughput and latency of the main memory system is much lower than the rate at which the CPU can execute instructions. This limits the effective processing speed when the processor is required to perform minimal processing on large amounts of data, the processor must continuously wait for data to be transferred to or from memory. As the difference between compute performance and memory performance continues to widen, many algorithms quickly become bound by memory performance rather than compute performance. This effect is known as the von Neumann bottleneck. When many abstract models of computation were created, compute performance was the bottleneck. As VLSI scaling and processor technologies have improved, we can perform computation at much faster rates than we can read from main memory. For example, the Intel Core2Duo Quad (QX9650) can perform computation at 96 GFLOPS and yet has  $\sim$ 5 GB/s of bandwidth to main memory. We have already passed an order of magnitude difference between our compute capability and bandwidth to main memory and the gap is continuing to widen.

Caches have reduced the effects of the von Neumann bottleneck, but in an effort to keep the computational units of the processor busy, processors have gained multiple levels of cache, thus building a memory hierarchy. Processors now have multiple levels of caches with high-bandwidth, low latency, but small caches close to the processor, and lower-bandwidth, higher latency, larger caches further away. For optimum performance, even on simple applications, the user must make efficient use of all the caches in the hierarchy. This is generally done by carefully blocking data into the caches to maximize the amount of reuse. For example, the first-order optimization effect for matrix multiply over the naive triple nested for loop implementation is to carefully block data for the cache hierarchy of the processor as well as the register file in the machine. This optimization accounts for the majority of the performance gain in this application for a single processor and will be explored further in the next chapter.

Several new architectures choose to directly expose the memory hierarchy instead of emulating the traditional von Neumann architecture. For example, graphics processors (GPUs) and the STI Cell Broadband engine (Cell) require explicit movement of data into memories visible to the processor. In the case of GPUs, data must be moved from node memory into the graphics memory on the accelerator board for algorithm correctness. The SPEs in the Cell processor can only directly reference data in their small local memories, and data must be explicitly DMAed in and out of these memories during algorithm execution. Architectures that require explicit data movement are referred to as *exposed communication architectures* in the literature. Programming models that depend on a single address space fail to map efficiently to these architectures. Carefully using the memory system is no longer just about performance optimization but is also required for correctness on these architectures.

For both cache based and exposed communication memory systems, accessing data in bulk is required to efficiently use the memory hierarchy, and over time bulk access only becomes more important because latencies are rapidly increasing with respect to processing speed. In exposed communication memory systems, bulk data access translates into bulk data transfers. Since just initiating a transfer can have a latency of thousands of cycles, it is wise to transfer as much data as possible for each initiated transfer to amortize the transfer cost. For example, the cost of issuing a DMA for a single byte from host memory into the local store of a SPE on the Cell processor has the same latency as a 1KB data transfer. In a cache hierarchy based systems, accessing data in bulk leads to spatial locality in the cache, more efficient cache line prefetching, minimal misses to higher levels of the memory hierarchy which have even more access latency, and the amortization of cache miss costs along the cache line. Furthermore, some architectures like GPUs achieve extremely high bandwidths by using high latency but wide memory interfaces. For example, AMD's R600 processor uses a 512-bit memory interface to achieve greater than 100 GB/s to graphics memory [AMD, 2007]. However, this performance requires a burst size of 256-bytes for each memory request to efficiently make use of the wide interface and the high degree of interleaving and banking in the memory system.

Ideally, we would like to maximize the computational and bandwidth utilization of our machine. If we can overlap computation and communication, we can maximize the use of both for a given application. On cache machines, this can be done with data prefetching; exposed communication memory systems can use asynchronous transfer mechanisms. For optimal performance, we want to prevent stalling the compute resources as much as possible. As such, we need to do our best to make sure the data is available before computation begins. This requires identifying the data that will be needed next and starting transfer of

Figure 2.1: Single threaded scaling performance has come to an end.

the data as early as possible in the algorithm. This formulation is sometimes referred to as a *streaming* formulation. In practice, either computational resources or bandwidth resources become the limiting performance factor in this style of computation.

#### 2.1.2 From Sequential to Parallel

As can be seen in Figure 2.1, performance scaling of single core performance according to Moore's Law has slowed considerably. Whereas single threaded performance has scaled at  $\sim$ 52% per year from the mid-1980s to 2001, Intel now projects only a  $\sim$ 10% performance increase each year in single threaded performance. Previous generations of processors have relied on progressively more advanced out-of-order logic, speculative execution, and superscalar designs along with increasing clock frequencies to continually increase performance of sequential, single threaded application performance. However, because of power and design limitations, we have largely hit the wall in scaling clock frequency, and superscaler processor design has reached the limit of available instruction level parallelism for most

programs. Future processor designs are shifting transistor resources into multiple simplified processors on a single die. The STI Cell is a somewhat extreme example as the cores are in-order, have no branch prediction hardware, and the simplest cores on the die, the SPEs, do not even contain support for caches and require explicit data movement. In many ways, the design of each core represents the state of the art in architecture from more than a decade ago, albeit at much higher clock frequencies. The upcoming Intel Larabee design is comprised of many massively simplified x86 cores [Carmean, 2007]. Simpler cores allow a much denser packing of compute resources. Doug Carmean, the architecture lead of the Larabee project, has proposed that four of these simpler cores can fit in the same space as a current Core2 generation core. Clock for clock, the Larabee cores also have four times the theoretical compute performance of the traditional x86 designs from Intel, but sequential, single threaded performance may be as low as 30% of the current Intel designs [Carmean, 2007]. The difficulty with this architecture trend is that for programmers to increase application performance, they can no longer rely on improvements in sequential performance scaling and they now have to be able to effectively use parallel resources.

Traditional parallel programming techniques are beginning to break down as systems are becoming more and more parallel. The latest shipping CPUs currently have four cores, but road-maps from the CPU vendors show that scaling is expected to continue at a rate matching Moore's Law, meaning that if this scaling holds, then consumers will see 64 cores by 2015 and upwards of 100 cores in high-end workstation machines. In the high performance computing space, supercomputers have become extremely large, with the top 10 supercomputers having more than eight thousand processors. Ideally, we would like to have programming solutions that allow parallelism to scale easily from small numbers of processing elements to many, allowing algorithms and applications designed today on several cores to scale up to many cores.

### 2.2 **Programming Systems**

There has been a great deal of research on parallel languages, with some efforts going back several decades. Parallel languages and programming have continued to come in and out of vogue, with the last major efforts being in the mid to late 1990s. Most languages have focused on the high performance computing (HPC) domain, e.g. scientific computing like that performed at the US Department of Energy. High-performance computing has gradually become more common place with more industries now relying on large numbers of processors for financial modeling, bioinformatics, simulation, etc. As people have begun to see the reality of scalar processor performance hitting a wall, exploring programming models and parallel programming in general are actively being researched again. The DARPA HPCS program is now funding several research programming systems that reduce the cost and programming difficulty, increase the performance on large machines, provide portability across systems, and increase robustness of large applications [DARPA, 2007]. GPUs have also driven research into stream programming and data parallel languages in order to efficiently use these high performance, but esoteric, architectures [Owens et al., 2008].

While there have been many languages for parallel computing, most applications in HPC rely on MPI for distributed memory machines and OpenMP for shared memory systems. In the mainstream computing/consumer space, threading APIs like PThreads remain the most common. Streaming languages, largely driven by the difficulty in programming GPUs for more general computation than just graphics, remain largely ignored by the programming community and have yet to be used in common consumer applications or code development. Each language closely matches the underlying architecture it was originally targeted for, making portability to different machines while maintaining performance challenging.

#### 2.2.1 **Programming Models**

#### **Random Access Machine**

The Random Access Machine (RAM) model [Aho et al., 1974] views a machine as a processor attached to a uniform and equal access cost memory system. A RAM is a multiple register machine with indirect addressing. Data access in a RAM program is modeled as instantaneous; thus, a processor never waits on memory references. The Parallel Random Access Machine (PRAM) model [Fortune and Wyllie, 1978] extends the RAM model to parallel machines. In a PRAM machine, data access from all processors to memory as well as synchronization between processors is modeled as instantaneous.

The RAM and PRAM models do not accurately model modern architectures. Even in a sequential system, data in the L1 cache can be accessed much faster than data in main memory, but all data transfers have some cost in terms of latency and are not instantaneous. Moreover, since data is transferred in bulk in modern architectures (cache-lines, memory-pages, etc.) locality of access is not taken into account in this model. Fine-grain, random data access is much more costly than bulk, coherent access because you can cause the memory system to load data in bulk (e.g. a cache-line of data) and then only use a small amount of the data loaded (e.g. a single byte of the cache-line). Despite only needing a small amount of data, the programmer pays for the bandwidth and latency of the larger transfer and can cause thrashing in the memory system. In the case of a parallel system, coherence protocols and non-uniform memory access (NUMA) designs further increase the cost of poor data access patterns. Moreover, the PRAM model treats synchronization can cost hundreds of cycles. Algorithms designed using these computational models tend to perform poorly on modern architectures.

However, the RAM and PRAM model provide a very simple abstraction for computation and the PRAM model aides in understanding concurrency. These models serve as good teaching tools for algorithms and computational complexity, but provide little insight into the most performance critical aspects of contemporary algorithm design and analysis.

#### **Bulk Synchronous Parallel**

The Bulk Synchronous Parallel (BSP) model [Valiant, 1990] differs from the PRAM model in that communication and synchronization costs are not assumed to be free. An important part of the analysis of programs written according to the BSP model is the quantification of the communication and synchronization during execution. A BSP program is comprised of three supersteps: 1) concurrent computation, 2) communication, and 3) synchronization. During the computation phase, the same computation occurs independently on all processors operating only on data local to each processor. During the communication phase, the processors exchange data between themselves en masse. During the synchronization phase, each processor waits for all other processors to complete their communication phase. Algorithms are comprised of many of these supersteps.

The main advantages of BSP over PRAM is that algorithms are comprised of separate computation, bulk communication, and synchronization steps. The programmer is made aware of the cost of communication and synchronization and is encouraged to transmit data in larger chunks. However, the BSP model as presented in the literature does not model memory hierarchies with more than two levels: main memory and processor memory.

#### LogP

The LogP model [Culler et al., 1993] is based on parameters that describe the latency (L), communication overhead (o), gap between consecutive communications (g), and the number of processor/memory models (P) of the machine. Compared to the BSP mode, the LogP model has more constrained communication mechanisms and lacks explicit synchronization, but allows for more flexible communication and execution capabilities. Unlike the BSP model, communication and computation are asynchronous, and a processor can use a message as soon as it arrives, not just at superstep boundaries. LogP works to encourage coordinating the assignment of work with data placement to reduce bandwidth requirements as well as encouraging algorithms that overlap computation and communication within the limits of network capacity.

Like BSP, LogP does not assume zero communication delay or infinite bandwidth, nor does it tailor itself to a specific interconnect topology as do simpler models. Implicit in the model is that processors are improving in performance faster than interconnect performance, and that latency, communication overhead, and limited bandwidths will be the performance critical aspects of algorithm design. However, like the BSP model, the LogP model models two level memory hierarchies and is really targeted towards modeling interconnected computers and not the full memory hierarchy of the machine. Some researchers have argued that the BSP model is a more convenient programming abstraction and computational model for parallel computation; however, the LogP model can be more exact in modeling some machines as compared to BSP [Bilardi et al., 1996].

#### **Cache Oblivious**

Cache oblivious algorithms are designed to exploit a cache hierarchy without knowledge of the specifics of the caches (number, sizes, length of cache lines, etc.) [Frigo et al., 1999]. In practice, cache oblivious algorithms are written in a divide-and-conquer form where the problem is progressively divided into smaller and smaller sub-problems. Eventually, the sub-problem will become small enough to fit in a cache level and further division will fit the problem into smaller caches. For example, matrix multiply is performed by recursively dividing each matrix into four parts and multiplying the submatrices in a depth first manner. However, for optimal code, the user must define a base case for the recursion that allows for an efficient implementation of the computation. In practice, the base case stops recursion after the data fits in the cache closest to the processor and an optimized function is written to optimize register usage and take advantage of available SIMD instructions. The elegance of cache oblivious algorithms is that they can make efficient use of the memory hierarchy in an easy to understand way. Accordingly, this is an attractive place to start the design of our system.

However, there are several issues with the cache oblivious approach. Firstly, the cache oblivious model makes the assumption that the memories are caches and that data at the base of the recursion can be accessed via global addresses. This model has problems on systems that have exposed communication hierarchies as the address spaces are distinct and cannot be accessed using global addresses. The cache oblivious model also relies on a memory system comprised of a cache hierarchy in which all data access can be driven from the bottom of the hierarchy and misses into a cache will generate requests into the cache above it and so on until the memory memory request can be satisfied and the data can be pulled into the lowest level cache. It also assumes that higher level caches are inclusive, i.e. they include all of the data in the caches below them. We must stall on every miss and

rely on low miss rates, which is the general case for optimal cache oblivious algorithms. However, since the data access is fine grained and generated from the bottom of the memory system, we do not have the ability to transfer data in bulk, required for efficient memory transfers on exposed communication hierarchies, nor the ability to prefetch data to avoid stalls and allow for overlapping computation and communication. Parallelism is also not able to be directly described in this model.

#### Streaming

The stream programming model is designed to directly capture computational and data locality. A *stream* is a collection of records requiring similar computation while *kernels* are functions applied to each element of the stream. A streaming processor executes a kernel for each element of the input stream(s) and places the results into the output stream(s). Similar to BSP, streaming computations are comprised of a communication phase to read inputs, a computation phase performing calculations across the inputs, and a communication phase placing the results into the outputs. However, unlike BSP, synchronization is not required as each stream element is executed on independently and communication does not exist between elements. Streaming formulations also have the benefit that the communication and computation phases are overlapped to maximize the resources of the machine. Also, stream programming encourages the creation of applications with high arithmetic intensity, the ratio of arithmetic operations to memory bandwidth [Dally et al., 2003], with the separation of computation into kernels applied to streams. The drawback of traditional streaming approaches is they only handle two levels of the memory hierarchy, off processor and on processor memory.

#### 2.2.2 **Programming Languages**

#### **Global View**

*Global view* languages allow for arbitrary access to the total system memory, providing RAM/PRAM models of computation. ZPL [Deitz et al., 2004], Chapel [Callahan et al., 2004], and High Performance Fortran (HPF) [Forum, 1993] are examples of global view languages. These three languages are array-based, borrowing from Fortran syntax. Since there are no pointers or pointer arithmetic, more aggressive compiler analysis is possible. All three languages allow the programmer to express parallelism via simple data parallel iteration constructs such as parallel for loops. The data parallel basis of these languages provides guarantees that there is no aliasing on writes to arrays and execution and control are defined in bulk, which allows for aggressive optimizations. Since synchronization primitives are not exposed to the user and there are guarantees about data aliasing, the compiler can be aggressive in scheduling by relying on data dependence analysis of the call chain.

A limitation of these languages is that there is no first class language support for specifying how to place data in the machine for locality. *Regions* combined with *distributions* in ZPL and Chapel provide information about what data is needed for a computation but not where that data resides. Regions do have the nice property that the area of memory that can be accessed is well defined so that memory movement can be scheduled in the case of distributed memory, but these languages do not provide a way to specify how data should be laid out to minimize communication. Furthermore, these languages have no notion of the memory hierarchy of the machine on which the code is executing and allow fine-grain data access to the global system memory. As mentioned above with the RAM/PRAM models, this can lead to inefficient data access. In theory, the region constructs from ZPL/Chapel could be nested in order to decompose the data, but the user would have to explicitly manage the decomposition for each target machine.

#### **Partitioned Global Address**

Partitioned Global Address Space (PGAS) languages have been the most successful parallel programming languages to date in terms of implementations available on many machines and user community size. For example, Unified Parallel C (UPC) [Carlson et al., 1999] is available on several supercomputers including the Cray X1 family and T3E series, as well as large cluster machines such as Blue Gene/L. Co-Array Fortran [Numrich and Reid, 1998], an extension of Fortran 95, is being studied for inclusion into the Fortran 2008 specification. Titanium [Yelick et al., 1998] is a Java-based language with similar properties to UPC.

The PGAS model presents two levels of the memory hierarchy: data is either *local* to a processor or *global* to all processors. PGAS languages can only capture locality in two levels of memory, limiting execution to architectures which can be abstracted as two level machines. The PGAS model also allow fine grain data access, making the generation of bulk data transfers difficult, thus leading to potentially inefficient execution on architectures such as distributed memory systems. Programmers specify whether data is local or global and can access each in standard C syntax. UPC has recently gained API functions to support bulk transfers via memcpy's to help improve performance across slower interconnects; however, the user must decide when they are going to use bulk transfers over fine grain data access. Similar extensions have been proposed for Titanium and Co-Array Fortran. The added performance of using these extended mechanisms come at the cost of portability as not all machines nor compiler/runtime implementations have support for these constructs.

In UPC 2.0, extensions for asynchronous bulk transfers have also been proposed, but the user is responsible for scheduling data movement.

PGAS models also have difficulty with memory coherence and consistency on machines that do not provide these capabilities in hardware. Since the machine is presented to the user as distributed shared memory, the user is responsible for synchronization, but memory consistency behavior is unclear in the general case ("relaxed consistency" in the UPC documentation) and behavior can vary between machine types. This leads to overzealous synchronization in user code, possibly sequentializing execution during large parts of the code. Another subtle issue with the current PGAS models is that they do not support nested-parallelism. As such, the nested parallel loops must be flattened into a single parallel loop by the user manually to increase parallelism.

#### **Threading languages**

Cilk [Blumofe et al., 1995] provides a language and runtime system for light-weight threading, which is particularly suited, but not limited, to cache-oblivious algorithms implicitly capable of using a hierarchy of memories. Cilk is a simple addition the the C programming language, and simple elision of Cilk programs can be compiled by standard C compilers and executed on sequential machines. The main difference between Cilk and C is the support for a fork/join execution model in Cilk. The user can spawn threads for computation using fork and then wait for thread completion with joins. Cilk relies on an efficient runtime system to spawn and schedule threads to processing elements.

Like C, the user is allowed to use fine grain memory access from global data and may run into the performance pitfalls of a random access memory model. Moreover, compiler optimizations are made difficult by potential pointer aliasing in the programmer's code. When code is written in a cache-oblivious manner, the behavior of the memory system can be vastly improved, but access is still fundamentally to the entire global memory. This limits efficient execution of Cilk to shared memory machines. However, Cilk's runtime system has the ability to better handle irregular computations than many other systems.

#### GPGPU

Given the promising computational capabilities of graphics processors, there have been several academic and industry efforts to create languages for general purpose computation on graphics processors (GPGPU). BrookGPU [Buck et al., 2004], a derivative of the Brook [Ian Buck, 2003] streaming language based on C with streaming extensions, is designed to abstract a graphics processor as a streaming processor. Data is explicitly transferred to and from host memory using streamRead and streamWrite operators to initialize streams of data. As a streaming computation model, the user defines kernels which operate over streams. The kernels are invoked once per output stream element and executed in a data parallel fashion with no communication or synchronization between kernel invocations. BrookGPU allows kernels to read from streams in a general way (gathers) but does not allow arbitrary writes to streams (scatter). The functional capabilities of BrookGPU directly correspond to what can be done using graphics APIs, and all runtime calls and kernels are mapped to graphics API primitives such as textures, framebuffers, and fragment shaders. BrookGPU is inherently a two level memory model with explicit data transfers: data is either in host memory or in device memory. However, there are multiple levels of cache and scratch-pad memories available on the latest GPUs that are not exposed via the programming model that can limit application performance.

Nvidia's CUDA [NVIDIA, 2007] programming language is based on C with extensions for data parallel execution. CUDA presents the GPU as a bag of parallel processors on which programs can be executed. Similar to BrookGPU, the user must explicitly transfer

data from host memory to device memory before program execution. However, CUDA does not use streaming semantics during program execution and instead uses explicit general reads and writes via pointers and arrays. The user describes an execution grid which specifies how many times to invoke the program in total creating the specified number of threads, and how to divide the execution grid into blocks of threads to be scheduled on the processor. Moreover, CUDA exposes small scratch-pads per processor that data can be explicitly read to and written from the program to allow data sharing between threads on a processor. This memory is not directly in a hierarchy, i.e. one cannot cause a transfer from device memory directly to the scratch-pad and instead must use registers as an intermediate and use two transfer operations. Thus, CUDA exposes three memories to the userhost, device, and scratch-pad. Another difference between CUDA and BrookGPU is that CUDA allows limited synchronization. Synchronization is defined for threads in a block allowing for data sharing and communication between threads via the scratch-pads. While there are claims of performance gains using this model, the user must explicitly code to the specific architecture implementations to use these more advanced features potentially limiting portability to other GPUs.

### 2.2.3 **Runtime Systems and APIs**

#### **Compiler** assisted

OpenMP is a successful system for parallelizing code via compiler hints on shared memory machines. Programmers write their code in standard programming languages like C, C++, and Fortran, and provide hints to the compiler via pragmas about which loops can be parallelized and how the execution of the loop should be distributed among processors. More aggressive compilers will attempt to automatically parallelize all loops. OpenMP is very attractive to programmers because they do not have to use a new programming language

or model and still get parallel code. The compilers must be conservative in parallelizing to maintain correctness but often struggle with pointer aliasing. The user must progressively add hints and/or re-factor their code to avoid the potential for aliasing and help expose more potential parallelism to the compiler in order to gain better performance. Unfortunately, the pragmas differ between compilers, although there is a standard subset which is generally used. Using the vendor specific extensions for better optimization and targeting of a specific machine come at the cost of portability. Moreover, in practice, the ability of OpenMP compilers to parallelize arbitrary code is very limited and users have to go through many iterations exploring pragmas and restructuring their code to allow the compiler to better parallelize.

OpenMP can be inefficient on large shared memory machines because of non-uniform memory access effects and makes distributed memory implementations problematic since there is no notion of locality and the model is built around fine-grain global data access. Since there are no direct methods for bulk data transfers, performance can suffer greatly across slow interconnects, or the user must reorder their code and add progressively more hints to get the compiler to generate code for efficient data transfers. OpenMP is also unable to provide asynchronous data transfers thus leading to a reactive memory system in the common case where a data access may cause a stall for an undefined amount of time. Some implementations can work around this by implementing user level threads on each execution unit and switching execution threads on expensive data transfers.

#### APIs

The Parallel Virtual Machine (PVM) [Geist et al., 1994] and MPI [MPIF, 1994], both preceded by [Su et al., 1985], are perhaps the oldest and most widely used systems for

programming parallel machines and are supported on many platforms. Both systems concentrate on the explicit movement of data between processors within one logical level of the machine. The user must specify all communication manually and communication requires both the sending and receiving node to be involved. The user must also explicitly control the creation of parallel contexts and all synchronization. MPI-2 [MPIF, 1996] adds support for single sided data transfer making programming easier, but these functions are not supported on all platforms. MPI-2 can also abstract parallel I/O resources, thus exposing another memory level, but the API is very different from the core communication API functions.

The Pthreads library allows direct programming of shared-memory systems through a threading model and also assumes a uniform global address space. The user is responsible for creation, destruction, and synchronization of all parallel contexts. Moreover, since by default all data in the parent process is shared by all threads, so the user is responsible for maintaining thread local storage and managing communication and synchronization between threads. Other two-level runtime systems include Charm++ [Kalé and Krishnan, 1993], Chores [Eager and Jahorjan, 1993], and the Stream Virtual Machine (SVM) [Labonte et al., 2004]. None of these systems are designed for handling more than two levels of memory or parallel execution in a unified way.

The IBM Cell SDK [IBM, 2007b] provides an API for programming for the IBM Cell processor. This API is a very low level programming interface closely matching the hardware and explicitly supports only two-levels of memory. The user must create and manage executions contexts on the SPEs, manage loading of executable code into the SPEs as overlays, communicate between the PPE and SPE, and control DMAs and synchronization. This API is unlike any of others described and provides yet another distinct programming system and mindset.

# Chapter 3

# **Abstract Machine Model**

In order to meet our goals of portability across machines while maintaining good performance, we need to find a computational model and machine abstraction that fits our needs. As discussed previously, modern architectures are gaining ever increasing amounts of parallelism (Section 2.1.2) and deeper memory hierarchies (Section 2.1.1). As such, we need to find a computational model that encapsulates the performance critical aspects of modern architectures. Also, since there are many different types of architectures, we need to find a uniform way to abstract machines.

Most theoretical machine models in computer science do not address certain performance issues important for creating high performance programs on modern architectures. Careful tuning of an algorithm to closely match the characteristics of the architecture can lead to more than an order of magnitude increase in program performance. Many performance tuning problems that arise after the algorithm and data structures have been chosen amount to efficiently moving data through the machine. Much of the large performance increase comes from taking into account the various aspects of the memory hierarchy of the target machine. However, this tuning requires detailed knowledge of the machine's architectural features.

Traditional models of computation, such as the Random Access Machine (RAM), ignore the non-uniform cost of memory access. For example, let us explore the performance of matrix multiplication to show the difference between theory and practice. In the RAM model, where every memory access is uniform, the complexity of this program is  $O(N^3)$ . Implementing the matrix multiplication in this model leads to the traditional naive triplenested for loop formulation. However, real contemporary systems have multiple levels of caching and requirements on alignment for performance and this formulation which are not well suited to this formulation. On an Intel 2.4 GHz Pentium4 Xeon machine, this naive implementation compiled with the Intel compiler performs a 1024x1024 matrix multiplication at 1/150th the performance of Intel's Math Kernel Library, more than two orders of magnitude lower performance. The performance of the naive implementation is limited by the latency and throughput of the last level of the memory hierarchy. However, if we take into account the memory hierarchy of this machine, we can greatly increase performance to the point where the actual performance better matches the performance of a highly tuned implementation.

The Intel Pentium4 Xeon processor has several levels of memory hierarchy as shown in Figure 3.1: a register file, a 32 KB L1 cache, a 512 KB L2 cache, and main memory. The register file is extremely fast but very small. As we get further away from the functional units, the larger the memory gets, but the lower the bandwidth and the higher latency becomes. We can start by first performing small blocked matrix multiply operations in closest/fastest memory, the register file, and then building the larger matrix multiply in terms of these smaller matrix multiplies. This leads to a 6-nested for loop implementation, a triple-nested for loop representing the 4x4 matrix multiplies fitting into the registers, and another triple-nested for loop which blocks the full matrix multiplication in terms of the

Figure 3.1: Intel Pentium4 Uniform Memory Hierarchy example

Figure 3.2: Optimizing matrix multiply for the memory hierarchy. Starting from a naive implementation, we can progressive add more optimizations and get to within 1/4 of the performance of the highly tuned MKL library with only memory system optimizations.

smaller 4x4 matrix multiplications. This adaptation to just explicitly take advantage of the fastest/lowest level of the memory hierarchy, without considering any other levels explicitly, increases performance to 1/22 of MKL, a performance increase of almost a factor of 7 with just this simple modification. Similarly, we can block for execution into the next level of the memory hierarchy, the L1 cache, performing 32x32 matrix multiplies comprised of 4x4 register matrix multiplies, by adding yet another set of triple-nested for loops. Blocking for the L1 cache increases performance by another factor of 2, to 1/10 of MKL performance. Blocking again for the next level of the memory hierarchy, the L2 cache, performing 256x256 matrix multiplies, increases performance to  $\sim 1/8$  of MKL performance. If we manually reformat the data to better match the cache line sizes of the processor and the data order in which the hardware prefetch units function, we can get within 1/4 of the performance of MKL. The performance effect of this progression of optimization is shown in Figure 3.2. Notice that we can achieve 1/4 of the performance of a processor vendor's code with only optimizations for the memory hierarchy. Hand-tuning the inner loop along with fairly heroic optimizations yields the remaining factor of 4 in performance.

## **3.1 Memory Hierarchy Model**

The matrix multiplication example motivates a programming model that captures the relevant performance aspects of the hierarchical nature of computer memory systems. The Uniform Memory Hierarchy (UMH) model of computation [Alpern et al., 1994] presents a framework for machines with more than two levels in the memory hierarchy. As a theoretical model, UMH refines traditional methods of algorithm analysis by including the cost of data movement through the memory hierarchy. However, the UMH model also provides a way to abstract machines as a sequence  $\langle M_0, \ldots, M_n \rangle$  of increasingly larger memory modules with computation taking place in  $M_0$ . For example,  $M_0$  may model the computer's central processor and register file, while  $M_1$  might be cache memory,  $M_2$  main memory, and so on including all levels of the memory hierarchy in a given machine. For each module  $M_n$ , a bus  $B_n$  connects it with the next larger memory module  $M_{n+1}$ . Buses between multiple memory levels may be active, simultaneously transferring data. Data is transferred along a bus in fixed-sized blocks. The size of these blocks, the time required to transfer a block, and the number of blocks that fit in a memory module increase as one moves up the memory hierarchy.

An important performance feature of the UMH model is that data transfers between multiple memory modules in the hierarchy can be active simultaneously. Hence, the UMH model accounts for overlapping computation and communication, leading to programs bound by memory performance or compute performance rather than the sum of communication and computation. The UMH model expresses the tight control over data movement and the memory hierarchy that is necessary for achieving good performance on modern architectures.

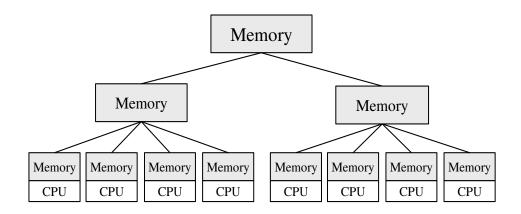

As mentioned in Section 2.1.2, we are quickly moving away from sequential processing to parallel processing. While the UMH model has been shown to be a good match for performance programming on sequential processors, it does not provide a solution for parallel processors. The Parallel Memory Hierarchy (PMH) model [Alpern et al., 1993] extends the UMH model for parallel systems. Instead of a linear connection of memory modules, the PMH model abstracts parallel machines as a tree of memory modules, see Figures 3.3 and 3.4. Similar to the UMH model's benefits over the RAM model of computation, the PMH model provides a better computational model than the Parallel Random Access Machine (PRAM) model. The PRAM model is a special case of the PMH model with only two levels of memory: a root memory module representing all of memory with p children each having a memory of size 1. The use of a tree to model a parallel computer's communication

Figure 3.3: Two level example of a Parallel Memory Hierarchy

structure is a compromise between the simplicity of the PRAM model and the accuracy of a arbitrary graph structure.

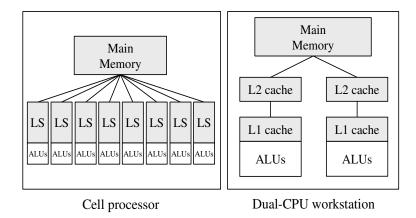

The PMH abstract representation of a system containing a Cell processor (at left in Figure 3.5) contains nodes corresponding to main system memory and each of the 256KB software-managed local stores (LSes) located within the chip's synergistic processing units (SPEs). At right in Figure 3.5, a PMH model of a dual-CPU workstation contains nodes representing the memory shared between the two CPU's as well as the L1 and L2 caches on each processor. The model permits a machine to be modeled with detail commensurate with the programmer's needs. A representation may include modules corresponding to all physical levels of the machine memory hierarchy, or it may omit levels of the physical hierarchy that need not be considered for software correctness or performance optimization.

## **3.2 Space Limited Procedures**

Space Limited Procedures (SLP) [Alpern et al., 1995] provides a methodology for programming in the PMH model and defines the general attributes of the underlying system.

Figure 3.4: Three level example of a Parallel Memory Hierarchy

Figure 3.5: A Cell workstation (left) is modeled as a tree containing nodes corresponding to main system memory and each of the processor's software-managed local stores. A representation of a dual-CPU workstation is shown at right.

SLP takes the PMH model and transforms the theoretical model into a methodology for obtaining portable high-performance applications.

To achieve high performance on a machine, the processing elements of that machine must be kept as busy as possible doing useful work. To keep processing elements busy, one must:

- decompose problems into independent sub-problems that can be executed concurrently,

- distribute these sub-problems among the processing elements in the machine,

- place necessary data as close to the processing element as possible, and

- overlap communication with computation when possible.

In SLP, each memory module can hold at least as much data as all its children combined and is parameterized by its capacity and the number of children it has. Data moves between a module and a child over a channel (bus) in fixed sized blocks. Each memory module runs a PMH routine that choreographs the flow of data between a module and its children and invokes PMH routines on its children. A problem instance begins in a memory module that is large enough to satisfy the application's storage requirements. The problem is then broken into sub-problems that can be executed using the storage available in the current module's children. Before a routine is invoked on the child, the input data must be present in the child memory module as well as storage available for the routine's results. Thus, the parent transfers data to its children, starts sub-problems in the children, waits for completion, and transfers the results back. These sub-problems are broken down further into progressively smaller sub-problems and passed down the tree of memories. Eventually, sub-problems small enough to fit into the leaves flow into the leaves where they are solved and their results are returned up the tree. The solutions to sub-problems may either be used as input to later sub-problems or passed up to the parent as part of the solution of the current problem. SLP programs are comprised of procedures that call procedures. The resulting call graph structure directly reflects the PMH tree structure representation of the target machine. Calls that can be executed in parallel may be identified explicitly or deduced via analysis. Alternative algorithms and/or data structures are indicated by overloading procedure names, thus providing multiple variants of the same procedure. Tuning parameters for space limited programs come in three forms: *machine parameters* are the parameters of the PMH model and reflect the performance relevant features of the target computer, *problem parameters* which defer other performance relevant choices until program specialization. Arguments to a procedure are identified as read, write, or readwrite.

The body of a variant of a space-limited procedure is composed of conventional programming language statements: control structures, procedure calls, and assignments. Arguments to the called procedure must take up substantially less space than those of the calling procedure. During specialization, the tuning parameters are defined, variants are chosen, and procedure calls are mapped to different memory modules in the machine.

## 3.3 The Sequoia Model