#### PROGRAMMING MANY-CORE SYSTEMS WITH GRAMPS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Jeremy Sugerman August 2010

#### Abstract

The era of obtaining increased performance via faster single cores and optimized single-thread programs is over. Instead, a major factor in new processors' performance comes from parallelism: increasing numbers of cores per processor and threads per core. At the same time, highly parallel GPU cores, initially developed for shading, are increasingly being adopted to offload and augment conventional CPUs, and vendors are already discussing chips that combine CPU and GPU cores. These trends are leading towards heterogeneous, commodity, many-core platforms with excellent potential performance, but also (not-so-excellent) significant actual complexity. In both research and industry run-time systems, domain-specific languages, and more generally, parallel programming models, have become the tools to realize this performance and contain this complexity.

In this dissertation, we present GRAMPS, a programming model for these heterogeneous, commodity, many-core systems that expresses programs as graphs of thread- and data-parallel stages communicating via queues. We validate its viability with respect to four design goals—broad application scope, multi-platform applicability, performance, and tunability—and demonstrate its effectiveness at minimizing the memory consumed by the queues.

Through three case studies, we show applications for GRAMPS from domains including interactive graphics, MapReduce, physical simulation, and image processing, and describe GRAMPS runtimes for three many-core platforms: two simulated future rendering platforms and one current multi-core x86 machine. Our GRAMPS runtimes

efficiently recognize and exploit the available parallelism while containing the foot-print/buffering required by the queues. Finally, we discuss how GRAMPS's scheduling compares to three archetypal representations of popular programming models: task-stealing scheduling, breadth-first scheduling, and static scheduling. We find that when structure is present, GRAMPS's adaptive, dynamic scheduling provides good load-balance with low overhead and its application graph gives it multiple advantages for managing the run-time depths of the queues and their memory footprint.

# Acknowledgements

My parents, Sharon and Art Sugerman, were enthusiastic and supportive when I ended more than five years of working full-time to seek a Ph.D. Nearly seven years later, they are still supportive, though in their own way each has made it clear that while they respected my disinclination to hurry, one is expected to graduate at some point. My advisor has made a similar point.

Speaking of which, I am very glad to have had Pat Hanrahan as my advisor. We have not always had an easy time understanding one another—despite both being fluent in Technical-Person English, our personal dialects are all but disjoint in some places—but we generally worked our way to common ground and I learned far more from the exposure to a mind and character I respected that was so different from my own. He indulged and abetted my masquerading as a graphics person, and even sort-of becoming one.

I am also grateful to Kurt Akeley and Mendel Rosenblum for serving on my reading committee and being excellent resources and role models. Kurt is an amazing engineer. It is a pleasure and an education to watch him digest a topic, talk, or paper and hear the content and phrasing of the questions he asks in the process. I owe Mendel an enormous debt of gratitude for many, many things: all his signatures my first pass at Stanford; VMware, plus his friendship and teaching there; support applying to grad school; and all the conversations and advice throughout school, even though we barely talked about my actual research.

Eric Darve and Christos Kozyrakis rounded out my orals committee. Eric unhesitatingly agreed to be my chair despite our only casual interactions. Christos not only welcomed my crashing of his group, but requested it, promoted GRAMPS, and pushed his students at me as collaborators. Additionally, John Gerth and a succession of capable admins in Gates 368—Heather, Ada, and Melissa—contributed tirelessly to making the lab, the infrastructure, and the paperwork all 'just work' when I needed anything.

I would also like to express appreciation for all the other students with whom I've had a chance to work. Daniel, Kayvon, Mike, Tim, and I all started together, worked with Ian on Brook, and with each other on various things. Kayvon and Tim, in particular, tolerated me many times and taught me a great deal. Solomon sneaked in a few years later, but was not too shabby, either. As mentioned, I also worked students of Christos: another Daniel, David, and Richard. They contributed heavily to work whose relevance to their own graduation was hazy and endured my cracks about computer architecture in academia with reasonable cheer.

Over most of the past seven years, Stanford was not my sole day job. Despite the fact that school consumed the lion's share of my attention, I was able to stay involved with VMware. Many people, but especially Paul Chan and later Steve Herrod, helped preserve a place for me and offer a refuge for my sanity when academic life got too... academic. In addition, the Stanford Graphics Lab enjoys privileged access to smart, capable, people in industry who were a huge help in my research and more generally my curiosity about neat technology. I am grateful to people from (at least) NVIDIA, Intel, and AMD. Nick Triantos, John Nickolls, Ian Buck, Doug Carmean, Eric Sprangle, and Danny Lynch all gave me significant amounts of their time at various points.

Finally, I am of course grateful to my funding agencies. Stanford awarded me an incredibly generous Rambus Stanford Graduate Fellowship. I received additional support under the general aegis of the Pervasive Parallelism Lab and the Department of the Army Research (grant W911NF-07-2-0027), as well as hardware donations from Intel, NVIDIA, and AMD.

To all of these people, as well as everyone whom I asked questions or who asked me questions: thank you. You made my time in graduate school a rare privilege.

# Contents

| $\mathbf{A}$ | bstra | ct                                 | V   |

|--------------|-------|------------------------------------|-----|

| $\mathbf{A}$ | ckno  | wledgements                        | vii |

| 1            | Intr  | roduction                          | 1   |

| <b>2</b>     | Par   | allel Programming Models           | 5   |

|              | 2.1   | Domain Specific Programming Models | 5   |

|              |       | 2.1.1 Real-Time Graphics Pipelines | 5   |

|              | 2.2   | General Purpose Programming Models | 6   |

|              |       | 2.2.1 Task-Stealing                | 7   |

|              |       | 2.2.2 Breadth-First                | 8   |

|              |       | 2.2.3 Static                       | 9   |

|              | 2.3   | Conclusion                         | 10  |

| 3            | The   | e GRAMPS Programming Model         | 11  |

|              | 3.1   | GRAMPS Design                      | 11  |

|              | 3.2   | A GRAMPS Example                   | 12  |

|              | 3.3   | Execution Graphs                   | 14  |

|              | 3.4   | Queues                             | 15  |

|              |       | 3.4.1 Packets                      | 16  |

|              |       | 3.4.2 Queue Sets                   | 16  |

|              | 3.5   | Stages                             | 18  |

|              |       | 3.5.1 Thread Stages                | 19  |

|   |          | 3.5.2                               | Fixed-Function Stages         | 20 |  |  |  |  |

|---|----------|-------------------------------------|-------------------------------|----|--|--|--|--|

|   |          | 3.5.3                               | Shader Stages                 | 20 |  |  |  |  |

|   | 3.6      | Comm                                | on Design Idioms              | 21 |  |  |  |  |

| 4 | Fut      | ure Re                              | ndering Architectures         | 23 |  |  |  |  |

|   | 4.1      |                                     |                               | 23 |  |  |  |  |

|   | 4.2      |                                     | round and Related Work        | 25 |  |  |  |  |

|   |          | 4.2.1                               | GPUs                          | 25 |  |  |  |  |

|   |          | 4.2.2                               | Graphics on Stream Processors | 26 |  |  |  |  |

|   | 4.3      | Applic                              | ation Scope                   | 27 |  |  |  |  |

|   |          | 4.3.1                               | Direct3D                      | 27 |  |  |  |  |

|   |          | 4.3.2                               | Ray Tracer                    | 28 |  |  |  |  |

|   |          | 4.3.3                               | Extended Direct3D             | 29 |  |  |  |  |

|   | 4.4      | Multi-                              | platform                      | 30 |  |  |  |  |

|   |          | 4.4.1                               | Hardware Simulator            | 30 |  |  |  |  |

|   |          | 4.4.2                               | GRAMPS Runtimes               | 32 |  |  |  |  |

|   | 4.5      | Perform                             | mance                         | 34 |  |  |  |  |

|   |          | 4.5.1                               | Scheduling                    | 34 |  |  |  |  |

|   |          | 4.5.2                               | Evaluation                    | 36 |  |  |  |  |

|   | 4.6      | Tunab                               | ility                         | 38 |  |  |  |  |

|   |          | 4.6.1                               | Diagnosis                     | 38 |  |  |  |  |

|   |          | 4.6.2                               | Optimization                  | 41 |  |  |  |  |

|   | 4.7      | Conclu                              | ision                         | 42 |  |  |  |  |

| J | <b>C</b> |                                     |                               | 45 |  |  |  |  |

| 5 |          | Current General-Purpose Multi-cores |                               |    |  |  |  |  |

|   | 5.1      |                                     | uction                        | 45 |  |  |  |  |

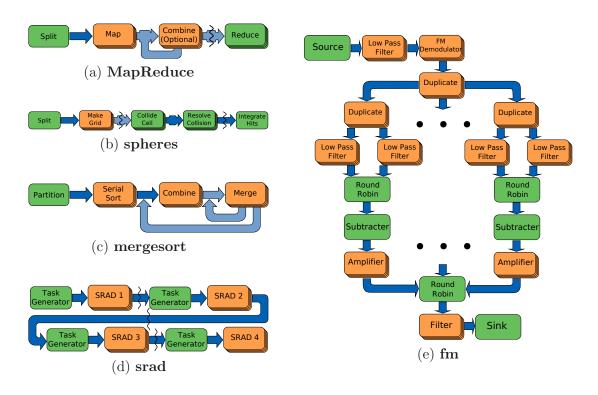

|   | 5.2      |                                     | ation Scope                   | 46 |  |  |  |  |

|   | 5.3      |                                     | platform (Implementation)     | 50 |  |  |  |  |

|   |          | 5.3.1                               | Data Queues                   | 50 |  |  |  |  |

|   |          | 5.3.2                               | Task Queues                   | 51 |  |  |  |  |

|   |          | 5.3.3                               | Termination                   | 52 |  |  |  |  |

|   | 5.4      | Perform                             | mance                         | 53 |  |  |  |  |

|              |      | 5.4.1 Scheduling                                  | 53 |  |  |

|--------------|------|---------------------------------------------------|----|--|--|

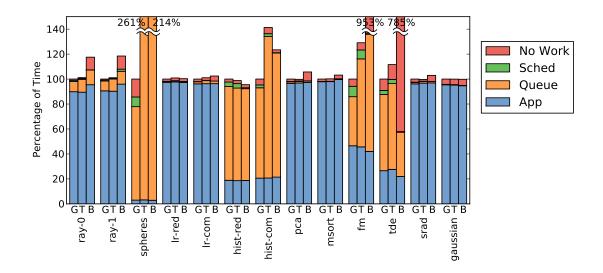

|              |      | 5.4.2 Evaluation                                  | 54 |  |  |

|              | 5.5  | Tunability                                        | 57 |  |  |

|              | 5.6  | Conclusion                                        | 58 |  |  |

| 6            | Con  | nparing Schedulers                                | 59 |  |  |

|              | 6.1  | Introduction                                      | 59 |  |  |

|              | 6.2  | Representing other Programming Models with GRAMPS | 60 |  |  |

|              | 6.3  | Evaluation                                        | 63 |  |  |

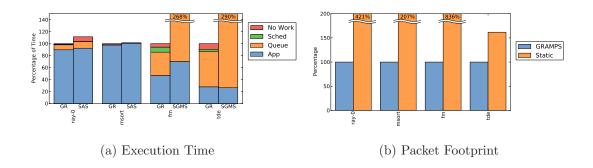

|              |      | 6.3.1 Execution Time                              | 64 |  |  |

|              |      | 6.3.2 Footprint                                   | 66 |  |  |

|              |      | 6.3.3 Static                                      | 68 |  |  |

|              | 6.4  | Conclusions                                       | 69 |  |  |

| 7            | Disc | cussion                                           | 71 |  |  |

|              | 7.1  | Contributions and Take-aways                      | 71 |  |  |

|              | 7.2  | Final Thoughts                                    | 73 |  |  |

| $\mathbf{A}$ | San  | aple GRAMPS Code                                  | 75 |  |  |

|              | A.1  | Application Graph Setup                           | 75 |  |  |

|              |      | A.1.1 C++ Setup                                   | 77 |  |  |

|              |      | A.1.2 Grampsh Setup                               | 79 |  |  |

|              | A.2  | Stages                                            | 80 |  |  |

|              |      | A.2.1 Generate-Keyed                              | 81 |  |  |

|              |      | A.2.2 Reduce-Huge-Reserve                         | 81 |  |  |

|              |      | A.2.2 Reduce-Huge-Reserve                         |    |  |  |

# List of Tables

| 2.1 | Summary of different general purpose programming models | 6  |

|-----|---------------------------------------------------------|----|

| 4.1 | Test scenes                                             | 36 |

| 4.2 | Simulation results                                      | 38 |

| 5.1 | Application characteristics                             | 47 |

| A.1 | The GRAMPS application graph API                        | 76 |

| A.2 | GRAMPS APIs for Thread and Shader stages                | 80 |

# List of Figures

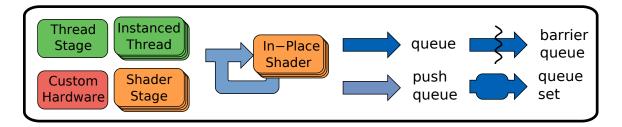

| 3.1 | Legend: the design elements of a GRAMPS program                              | 12 |

|-----|------------------------------------------------------------------------------|----|

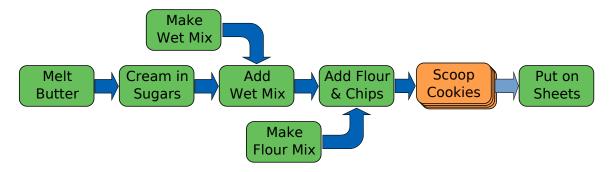

| 3.2 | Hypothetical GRAMPS cookie dough application                                 | 13 |

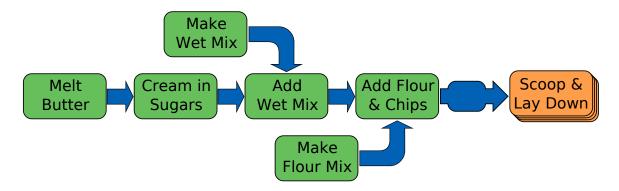

| 3.3 | Using a queue set                                                            | 17 |

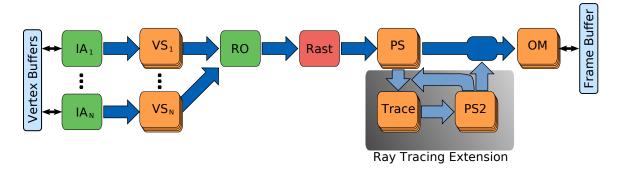

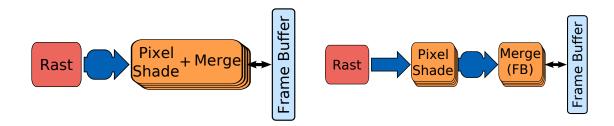

| 4.1 | Our Direct3D-based pipeline including optional extension                     | 26 |

| 4.2 | Our ray tracing application graph                                            | 27 |

| 4.3 | The CPU-like and GPU-like simulator configurations                           | 32 |

| 4.4 | The static stage priorities for the ray tracing application graph. $$ . $$ . | 34 |

| 4.5 | Grampsviz ray tracing the Teapot scene                                       | 39 |

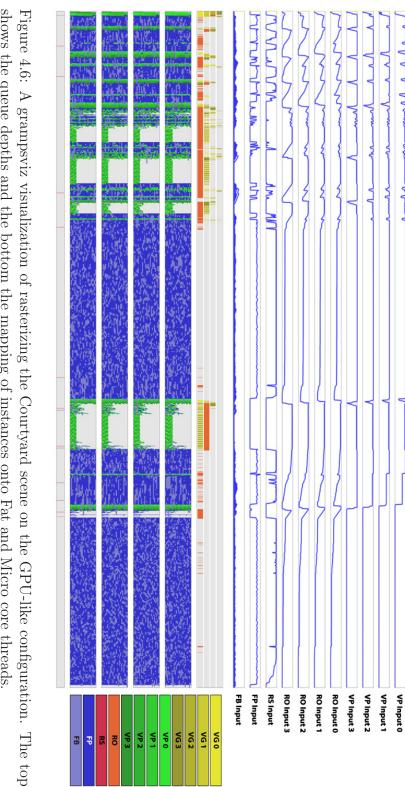

| 4.6 | Grampsviz rasterizing the Courtyard scene                                    | 40 |

| 4.7 | Initial and revised versions for the bottom of our Direct3D pipeline         | 41 |

| 5.1 | GRAMPS graphs for MapReduce, spheres, fm, mergesort, and                     |    |

|     | srad                                                                         | 48 |

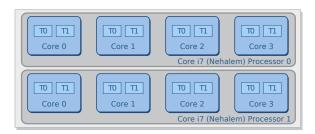

| 5.2 | Our two quad-core HyperThreaded test system                                  | 54 |

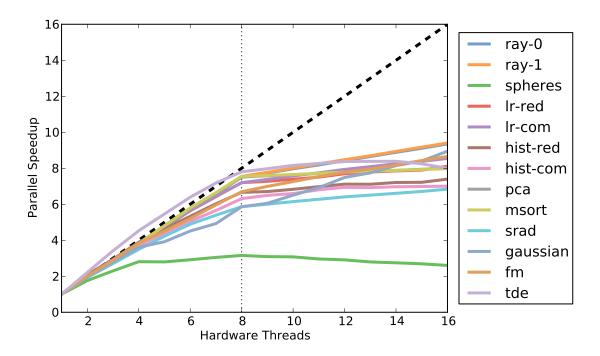

| 5.3 | Application speedup on an 8-core, 16-thread system                           | 55 |

| 5.4 | Execution time profile (8 cores, 16-threads)                                 | 56 |

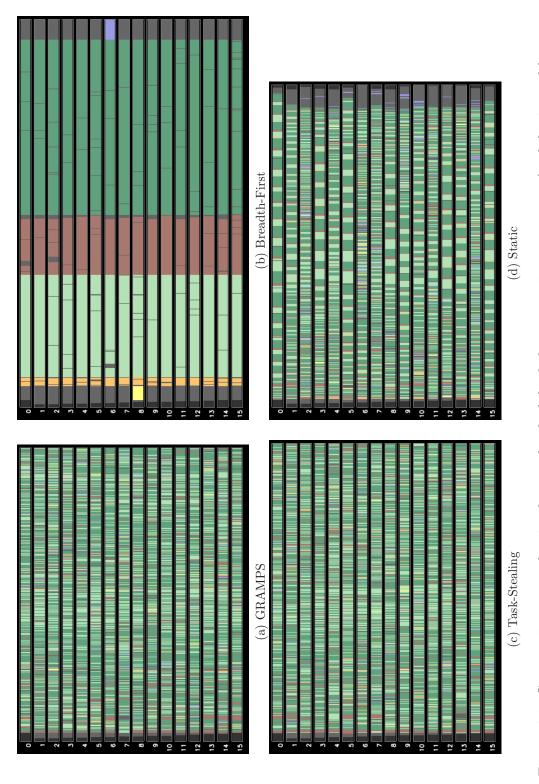

| 6.1 | Grampsviz output for our four schedulers                                     | 61 |

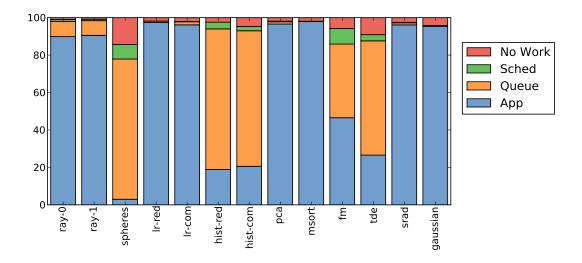

| 6.2 | Execution time profile (8 cores, 16-threads) of applications running the     |    |

|     | GRAMPS, Task-Stealing, and Breadth-First schedulers (left to right).         | 64 |

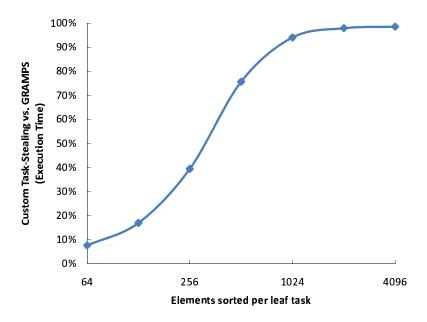

| 6.3 | Execution time by task size (GRAMPS versus tasks)                            | 65 |

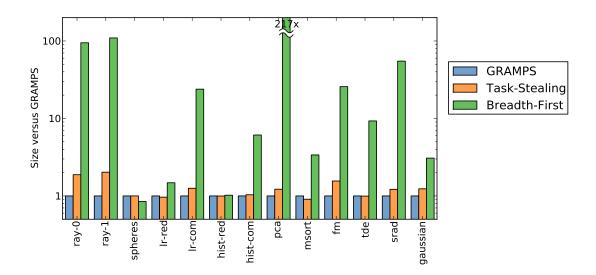

| 6.4 | Relative data queue depths for GRAMPS, Task-Stealing, and Breadth-           |    |

|     | first                                                                        | 66 |

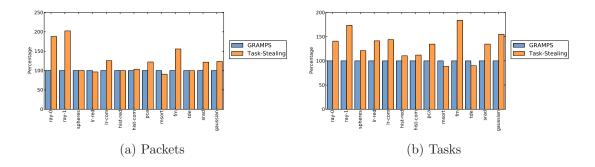

| 6.5 | Relative footprints of GRAMPS and Task-Stealing | 67 |

|-----|-------------------------------------------------|----|

| 6.6 | Static scheduling results                       | 68 |

| A.1 | Application graph for <b>set-reduce-keyed</b>   | 76 |

# Chapter 1

#### Introduction

Commodity computing and computers are in the midst of transition: the era of the single fast core is over. Multi-core CPUs are now prevalent and core counts are increasing in accordance with Moore's Law. Five years after the first dual-core x86 chips appeared, eight and twelve-core versions have been released. The rapid rise of independent cores per chip has made software parallelism critical to performance: scale-up, maximizing a core's utilization, was once paramount, but it is now rivaled or surpassed by scale-out, maximizing incremental performance as more cores are employed. Quite simply, with eight or twelve cores, realizing 80% performance from all of them dwarfs realizing 95% performance from only one.

Over the same period, the competing design pressures of power consumption and performance have increasingly promoted diverse heterogeneous platforms: different mixtures of different kinds of 'cores'. Programmable GPU cores originally designed for shading are now used to accelerate general purpose (i.e., non-graphics) applications by more than order of magnitude relative to conventional CPU cores in the same cost/design envelope. CPU designers are experimenting with their own trade-offs in core design. The Cell processor and Intel's Larrabee (now Knights) architecture both offer high computational abilities by using many copies of a simple core design in place of fewer copies of a state-of-the-art out-of-order superscalar processor [35, 40]. Additionally, the fact of multiple cores on the same chip, as opposed to multiple chips, has the potential to facilitate heterogeneity: so long as one core on the chip

can bootstrap the machine, the others can be more specialized. This has CPU vendors pursuing future chips that contain both conventional processors and GPU cores [1].

These impending heterogeneous, many-core, commodity machines offer enormous amounts of potential computational resources. Actually exploiting that potential, however, is a nontrivial challenge. Both parallelism and, especially, heterogeneous parallelism are major challenges for software development. Tackling them has created renewed interest in both academia and industry for developing high-level programming models, such as OpenCL [23], Cilk [15], and OpenMP [13]. High-level programming models provide two major advantages over low-level interfaces such as threads and locks. First, they provide constructs that make it easier for programmers to express parallelism. Second, their runtimes and schedulers manage concurrency and communication, simplifying these burdens for the programmer. This thesis introduces GRAMPS, a new high-level programming model for heterogeneous, parallel systems.

High-level programming models achieve their advantages by placing the application-programming model boundary closer to application constructs than hardware interfaces. This gives them more insight into application structure, patterns, and semantics. In exchange, they must make/impose assumptions about the chief types of applications and developers that they target.

Our application focus stems from three beliefs: interesting applications have irregularity; large bundles of coherent work are efficient; and the producer-consumer/pipeline idiom is important. These beliefs are rooted in our experiences, positive and negative, with graphics workloads and wrestling with graphics hardware for GPGPU purposes, but also draw upon our exposure to streaming architectures (and traditional parallel programming for CPUs). Irregularity takes many forms: different input elements may take different lengths of time to process, generate different numbers of outputs or different communication patterns, etc. At the same time, coherency enables amortization: it is more efficient to make one scheduling decision for one thousand items than one for each; to use SIMD execution to process a batch of items at a time; or to group work by access pattern for memory system locality. Finally, many workloads generate significant quantities of temporary/intermediate data during computation

that can be consumed incrementally as it appears. Not only does this allow parallelism of production and consumption, it has a powerful effect on locality: the data can be processed without the bandwidth and storage costs of spilling it to buffer in the higher levels of the memory hierarchy. We will (re)build program coherence dynamically by having the application expose related work to GRAMPS, which will aggregate it.

Our developer focus is systems-savvy developers: programmers who are well informed about their hardware and the best practices for it, but who dislike rote and prefer to use and build tools that systematize those idioms instead. A particular characteristic of this audience that influences our design in multiple places is a preference for the option of trading conservative guarantees for expressiveness. That is, a few sharp edges, if well-identified, optional, and powerful when used appropriately, are preferable to philosophically disallowing them for safety.

This thesis makes three main contributions:

- 1. The definition and design of GRAMPS (Chapter 3): programs as graphs of independent stages connected via queues; queues with application specified capacities and packet (work) sizes; and stages with can support no, limited, or total automatic intra-stage parallelism with static, conditional, or in-place (reduction) outputs.

- 2. Validation of GRAMPS with respect to four design goals (Chapters 4, 5, 6):

- Broad application scope: It should be possible to express a wide range of algorithms in GRAMPS and more convenient and effective than roll-your-own approaches.

- Multi-platform applicability: GRAMPS should suit a wide range of heterogeneous, many-core, commodity configurations.

- **Performance:** Applications built in GRAMPS should give up little performance over native implementations, specifically in terms of scale-out parallelism and buffering of intermediate data.

- **Tunability:** Developers should be able to become experts in GRAMPS, i.e., be able to explain the performance of their applications and be able to tune (optimize) them by adapting their use of the programming model.

- 3. Demonstration that GRAMPS performs better than current general-purpose programming models, with respect to the important metric of memory allocated to queues, without giving up performance (Chapter 6).

Tunability perhaps seems incongruous to have as such a prominent design goal. We believe it is absolutely critical for our audience: an un-tunable system is a system which can have no expert users (by definition) and heterogeneous, parallel programming is too complex to fully automate. Skilled developers will always know more about their workloads than any programming model can capture or infer. They will expect to have to optimize and refine their programs to employ that knowledge and will have little use for any tool that does not embrace that process.

Boiled down, these contributions amount to two things: (i) GRAMPS is a viable programming model for many applications on current and likely future machines; (ii) GRAMPS can be implemented to achieve good parallel scalability while keeping a low queue (memory) footprint. After a background discussion of current parallel programming models (Chapter 2) and a detailed overview of GRAMPS (Chapter 3), these assertions are validated by three case studies: GRAMPS for simulated future graphics architectures (Chapter 4), GRAMPS for current multi-core x86 machines (Chapter 5), and a horizontal comparison to schedulers based on alternative programming models (Chapter 6). We end with some overall discussion (Chapter 7) and provide a sample GRAMPS application as an appendix (Appendix A).

# Chapter 2

# Parallel Programming Models

This thesis proposes GRAMPS as a new programing model for parallel applications, but there are many existing ones. This chapter surveys the alternatives and identifies their defining properties.

#### 2.1 Domain Specific Programming Models

Programming models are able to simplify development and accelerate and/or manage applications by imposing and systematizing assumptions about their behavior. One common and effective way to do this is to restrict the supported application domain: this enables data types, synchronization primitives, and scheduling to be tailored to application semantics. Domain specific programming models are widespread, and range from long-lasting formalized models such as SQL for databases [45] to more one-off ad hoc models such as the plugin interfaces for web browsers (e.g., [28]).

#### 2.1.1 Real-Time Graphics Pipelines

The most relevant examples to GRAMPS are the rendering-specific programming models of OpenGL and Direct3D [39, 5]. These two, which are very close to each other, provide developers a simple, vendor-agnostic interface for describing real-time graphics computations. More importantly, the pipeline and programmable shading

| Model         | Supports<br>Shader | Producer-<br>Consumer | Hierarchical<br>Work | Adaptive<br>Scheduling | Examples          |

|---------------|--------------------|-----------------------|----------------------|------------------------|-------------------|

| Task-Stealing | No                 | No                    | No                   | Yes                    | Cilk, TBB, OpenMP |

| Breadth-First | Yes                | No                    | Yes                  | No                     | CUDA, OpenCL      |

| Static        | Yes                | Yes                   | Yes                  | No                     | StreamIt, Imagine |

| GRAMPS        | Yes                | Yes                   | Yes                  | Yes                    | _                 |

Table 2.1: Summary of different general purpose programming models.

abstractions exported by these interfaces are generally backed by highly-tuned GPU-based implementations. By using rendering-specific abstractions (such as vertices, fragments, and pixels) OpenGL/Direct3D maintains high performance without introducing difficult concepts such as parallelism, threads, asynchronous processing, or synchronization. The drawback of these design decisions is limited flexibility. Applications must be restructured to conform to the pipeline that OpenGL/Direct3D present. A fixed pipeline makes it difficult to implement many advanced rendering techniques efficiently. Extending the graphics pipeline with new domain-specific stages or data flows to provide new functionality has been the subject of many proposals, for example, [5, 18, 4], but their availability is gated by their endorsement, adoption, and release by the OpenGL/Direct3D model owners. In the first case study, we will look closely at using GRAMPS to implement a graphics pipeline more flexibly. In fact, one of the early motivations that led to GRAMPS was to enable "non-owners" of OpenGL/Direct3D to make performance-efficient adjustments to the graphics pipeline.

#### 2.2 General Purpose Programming Models

Other types of parallel programming models aim to be general purpose. They make simplifying assumptions/gain workload insight with higher-level operations and data-structures than raw kernel threads and locks, but avoid explicit expectations coupled to a particular application domain.

There are a great many general purpose parallel programming models, but we believe they mostly fit into three broad categories—Task-Stealing, Breadth-First, and Static—which we name in terms of their scheduling policies and for which we can identify canonical traits. While we will discuss particulars of specific implementations below, they have significant biases that complicate direct comparisons (due to unevenly tuned runtimes, different toolchains, varying benchmark implementations, etc.). Our primary objective is to distill the key scheduling policies, which we will use to compare them with GRAMPS and each other in Chapter 6.

Table 2.1 summarizes the three canonical models (and GRAMPS) according to four criteria:

- Support for shaders: The model provides a built-in construct for data-parallel kernels, which are automatically parallelized.

- Support for producer-consumer: The runtime is aware of data produced as intermediate results (i.e., created and consumed during execution) and attempts to exploit this awareness during scheduling.

- **Hierarchical work**: The model allows work to be expressed at different granularities rather than all being expressed at the finest granularity.

- Adaptive scheduling: The scheduler makes use of information available at runtime, and can choose from all available work to execute.

#### 2.2.1 Task-Stealing

Task-Stealing models are characterized by an underlying pool of threads that execute work which the application explicitly divides into independent *tasks*. Each thread has a queue of ready tasks, to which it enqueues and dequeues work. For load balance, when a thread's local queue is empty, it tries to steal tasks from other threads. Task-Stealing is a common low-level scheduling technique implemented by several runtimes, such as Cilk [15], TBB [21] and OpenMP [13].

Task-Stealing runtimes often focus on low-overhead task creation and execution in order to exploit fine-grain parallelism [3]. As a result, they tend to avoid any features that add per-task overhead, such as priorities, dependencies, or hierarchies. Rather,

they operate on 'task soup', a sea of equivalent-looking tasks. Since Task-Stealing systems offer minimal flow control or synchronization builtins, applications often roll their own locks and other primitives, which are then opaque to the programming model.

Task-Stealing models do not aggressively try to minimize memory footprint, but some provide guarantees that memory footprint grows at most linearly with the number of threads (e.g., by restricting which tasks to steal and using LIFO task queues [15]).

Thus, in terms of the criteria of Table 2.1, Task-Stealing only exhibits adaptive scheduling. Models can, and are designed to, schedule whatever tasks they believe enhance load-balance. The tasks, however, are essentially unstructured: all are equal in the eyes of the scheduler without any notion of grouping for hierarchy or recognizing producer-consumer behavior and without any support for automatic data-parallelism.

#### 2.2.2 Breadth-First

Breadth-First models are fundamentally about simple data-parallelism. They express programs as a sequence (DAG or pipeline) of implicitly data-parallel kernels and run one kernel at a time, with the runtime automatically instancing and managing enough independent copies of the kernel to utilize the available hardware resources. Data-parallel algorithms initially arose in the context of massively parallel supercomputers, such as the Connection Machine [19], and were exemplified by programming models/languages such as C\* [38]. The archetypal current Breadth-First models are those arising from GPGPU programming (using GPUs for non-graphics general purposes), such as OpenCL and CUDA [23, 31].

Executing one kernel at a time with barriers between stages/passes is straight-forward to implement (and understand), and highly effective for regular, divide-and-conquer, algorithms. Breadth-First's two weaknesses, though, are footprint and load-balance in the presence of irregularity. Scheduling breadth-first is the opposite of producer-consumer: the entire output of one kernel must be accumulated and buffered before any can be consumed by the next and no pipeline parallelism can be used to

overlap stages that cannot by themselves fill a machine.

Referring back to Table 2.1, Breadth-First models excel at shader support and include some hierarchical notion of execution: processing is expressed in terms of kernels launched on large input data sets with the fine-grained divisions onto hardware resources handled internally. As mentioned above, though, producer-consumer communication between kernels is completely impossible. And scheduling, while potentially somewhat dynamic in the dispatching of intra-kernel threads/instances, is not adaptive: no matter how plentiful the work available for other kernels is, only one kernel runs at a time.

#### 2.2.3 Static

Static models are very similar to GRAMPS, only scheduled according to offline/up-front transformations and decisions rather than dynamically. Applications are expressed graphs of stages that explicitly interact via data streams. The programming model automatically instances them and attempts a layout that exploits producer-consumer locality. They trade the adaptability of dynamic scheduling for up-front transformations to maximize run-time computational density. The (offline) scheduler needs full *prior* knowledge of the execution requirements of each stage and their cross-stage communication patterns, which are obtained from the compiler, a profiler, and/or user annotations. These models are typified by streaming systems, such as StreamIt [43] and architectures like Imagine [22], Merrimac [11], and RAW [44]. Unsurprisingly, their biggest weakness is handling irregularity/input-dependent workloads where execution behavior, communication patterns, or both, are impossible to approximate or know in advance.

Static models fulfill three of the four criteria used in Table 2.1: all but adaptive scheduling. From an application development perspective, they extend Breadth-First to add a full execution graph and allow overlapping of stages (i.e., kernels), and thus capture producer-consumer interactions. From an implementation perspective, however, Static models are entirely distinct: as its name implies, the entire execution order is predetermined before execution begins, the opposite of adaptivity.

#### 2.3 Conclusion

The primary advantages programming models offer come from the unifying/simplifying assumptions they make in the constructs they expose and the resulting leverage that gives them for implementation and scheduling. Making highly domain-specific assumptions has allowed very efficient, high performance implementations of real-time graphics pipelines on GPUs. At the same time, encoding application-domain traits naturally interferes with extending or modifying the range of applications well-suited to a model. In the next chapter, the first case study, we will look at using GRAMPS as an intermediate layer upon which the real-time graphics pipeline can be an application and use this indirection to both extend it and replace it completely.

There is also a diverse array of general purpose programming models. Among those relevant to our focus, we feel they group roughly into three canonical representatives: Task-Stealing, Breadth-First, and Static. Task-Stealing focuses on lightweight tasks and adaptive scheduling, Breadth-First focuses on data-parallelism, and Static focuses on regular/predictable execution graphs. Each fulfills a different subset of the key criteria we see for GRAMPS: support for shaders; support for producer-consumer; constructs for hierarchical work; and adaptive scheduling (Table 2.1). In Chapter 6, the third case study, we will compare GRAMPS and all three alternatives to show the impact of each criterion.

### Chapter 3

# The GRAMPS Programming Model

This chapter describes the GRAMPS programming model and its abstractions. It does not include execution details, such as scheduling algorithms, which are traits of particular implementations of the programming model. Those are described in the case studies in the subsequent chapters. Most of the programming model description has been published previously in [41] and/or [42].

#### 3.1 GRAMPS Design

GRAMPS is a General Runtime/Architecture for Many-core Parallel Systems. It defines a programming model for expressing pipeline and computation-graph style parallel applications. It exposes a small, high-level set of primitives designed to be simple to use, to exhibit properties necessary for high-throughput processing, and to permit efficient implementations. We intend for GRAMPS implementations to involve various combinations of software and underlying hardware support, similar for example, to how OpenGL permits flexibility in an implementation's division of driver and GPU hardware responsibilities. However, unlike OpenGL, we envision GRAMPS as being without ties to a specific application domain. Rather, it provides a substrate upon which domain-specific models can be built.

Figure 3.1: Legend: the design elements of a GRAMPS program.

GRAMPS is organized around the basic concept of application-defined independent computation stages executing in parallel and communicating asynchronously via queues. This relatively simple producer-consumer idiom is fundamental across a broad range of throughput applications. In keeping with our goal of domain independence, GRAMPS is designed to be decoupled from application-specific semantics such as data types and layouts and internal stage execution. It also extends these basic constructs to enable additional features such as limited and full automatic intrastage parallelization and mutual exclusion. With these, we can build applications from many domains: rendering pipelines, MapReduce, sorting, signal processing, and others. Figure 3.1 enumerates the building blocks of a GRAMPS application and will serve as a legend for all of the GRAMPS application graphs in this thesis. The rest of this chapter will first go through a non-technical example to help build an intuition and then describe GRAMPS's components in technical detail. In addition, Appendix A enumerates the precise interface our GRAMPS implementations export and provides the full contents of one of our regression tests as an example.

#### 3.2 A GRAMPS Example

Figure 3.2 shows a (hypothetical) GRAMPS graph for making chocolate chip cookies. Rather than diving into a highly technical workload, this more approachable example is useful for explaining the highlights of the programming model. As shown, dough preparation is broken into individual stages corresponding to logical steps in

Figure 3.2: A hypothetical GRAMPS graph for preparing chocolate chip cookie dough.

the recipe [7]. Each stage sends its output downstream and takes as input the ingredients and/or batter from its prior stage(s). Most of the stages are Thread stages (serial) because they combine (mix/blend/cream) their inputs, but cookie scooping is a Shader (data-parallel): as many chefs as are available can all independently take a blob of dough and form it into cookies simultaneously. Since each can make cookies of different sizes and shapes, the stage uses push for output, which enables conditional and variable output. Note that, in this formulation, the formed cookies have to serialize to be placed on the cookie sheets for baking: this spares the data-parallel scoopers from synchronizing or colliding when accessing the shared cookie sheets, but also constrains the overall parallelism. Section 3.4.2 describes queue sets, which improve this situation, and shows an enhanced cookie dough graph 3.3.

Cookie dough preparation also presents a straightforward physical analog for considering queue footprint: counter space. Any staged ingredients and partially finished batches of batter need to be set aside until it is time to use them. And, in every kitchen where we have cooked, counter space is *always* at a premium. This provides a strong incentive to prepare the batter (schedule the graph stages) in an order that leaves minimal pending dishes and bowls to fit on the counters (buffer in the queues).

Similarly, the granularity with which the recipe (and all recipes) is designed illustrates another significant aspect of GRAMPS: the concept of an efficient, but natural, work size that motivates the packet-based organization of queues and dispatching of stages. The author of the recipe (designer of the GRAMPS graph) chooses quantities

for one batch that roughly fill the bowls, measuring utensils, etc. of the target bakers (caches, SIMD widths, etc. of the available cores). And, while a baker would likely scale up or down a little, for example, to double or halve a recipe, he or she is unlikely to expend the effort to prepare a batch scaled down to a single cookie and would likely split preparation into multiple batches rather than attempt a single tenfold-recipe.

#### 3.3 Execution Graphs

GRAMPS application are expressed as execution graphs (also called computation graphs). The graph defines and organizes the stages, queues, and buffers to describe their data flow and connectivity. In addition to the most basic information required for GRAMPS to run an application, the graph provides valuable information about a computation that is essential to scheduling: insights into the program's structure. These include application-specified limits to the maximum depth for each queue, which stages are sinks and which sources, and whether there are limits on automatically instancing each stage. We have built a few different ways for developers to create execution graphs, all of them are wrappers around the same core API: an OpenGL/Streaming-like group of primitives to define stages, define queues, define buffers, bind queues and buffers to stages, and launch a computation.

Note that GRAMPS supports general computation graphs to provide flexibility for a rich set of algorithms. Graph cycles inherently make it possible to write applications that loop endlessly through stages and amplify queued data beyond the ability of any system to manage. Thus, GRAMPS, unlike pipeline-only APIs, does not guarantee that all legal programs robustly make forward progress and execute to completion. We have intentionally designed GRAMPS to encompass a larger set of applications that run well, at the cost of allowing some that do not.

Forbidding cycles would allow GRAMPS to guarantee forward progress—at any time it could stall a stage that was over-actively producing data until downstream stages could drain outstanding work from the system—at the expense of excluding some irregular workloads. Many of the GRAMPS versions of the applications in Chapters 4 and 5 contain cycles in their graph structure. Sometimes cycles can be

3.4. QUEUES

eliminated by "unrolling" a graph to reflect a maximum number of iterations, bounces, etc. However, not only is unrolling cumbersome for developers, it is awkward in irregular cases, such as when different light rays bounce different numbers of times depending on what objects and materials they hit. While handling cycles increases the scheduling burden for GRAMPS, it remains possible to effectively execute many graphs that contain them. We believe that the flexibility that graphs provide over pipelines and DAGs outweighs the cost of making applications take responsibility for ensuring they are well-behaved. The right strategy for notifying applications and allowing them to recover when their amplification swamps the system is an interesting avenue for future investigation.

#### 3.4 Queues

GRAMPS queues provide the means by which the (independent) GRAMPS stages communicate and exchange data. Each queue has two key application-specified traits: its packet information—the type and granularity at which it handles data—and its capacity—the maximum number of packets it can contain at any one time. Capacity is an important knob the application can use to throttle a point in the execution graph, for example because it has application specific knowledge about where work is represented most compactly or where a producing stage will often outpace its consumers. Note that it is an optional knob, however: the schedulers in all of our GRAMPS implementations have various domain-oblivious heuristics for managing queue depths that handle most situations well. When developing applications, we generally start each queue with a large capacity and only need to tune one or two strategic places in the graph.

In order to support applications with ordering requirements (such as OpenGL or Direct3D), GRAMPS queues can also be specified as strictly FIFO. With multiple or instanced consumers, this incurs two kinds of overheads: reduced parallelism as out-of-order packets stall until the in-order stragglers arrive, and extra storage to buffer and reorder the delayed packets.

#### 3.4.1 Packets

As mentioned above, the basic unit with which stages enqueue and dequeue work is called a packet. Each queue has its own packet layout, whose composition is application-specified. Packets are intended to allow application logic to collect and expose bundles of related work for efficient processing, for example, to amortize enqueue/dequeue operations, to fill hardware SIMD lanes, or to increase memory coherence/locality benefits. At the same time, in regions of the graph that are not performance critical, the application is free to use packets as small as it wishes. There are also often natural granularities to an algorithm itself, as with the cookie dough example.

GRAMPS imposes as few constraints on packet composition and layout as it can, so as to preserve application flexibility and keep its own interfaces simple. Packets have one of two high-level formats, defined as part of queue creation:

- Opaque: Opaque packets contain work that GRAMPS has no need to interpret. The application graph specifies only the size of Opaque packets (so GRAMPS can enqueue and dequeue them). Their contents are entirely defined and interpreted by the logic of stages that produce and consume them.

- Collection: Collection packets are for queues with at least one end bound to a data-parallel GRAMPS Shader stage. They represent a shared header together with a set of independent data elements which GRAMPS will dispatch as a unit. Collection packets specify three sizes: the packet size, the header size, and the per-element size. Additionally, GRAMPS reserves the first word of the header as a count of valid elements in the packet. Beyond that, the internal layout of elements and any addition header fields are opaque to GRAMPS.

#### 3.4.2 Queue Sets

The cookie dough graph in Figure 3.2 exhibits a common serialization problem: independent parallel processing followed by synchronization for distribution using a shared resource. In this case, packets of dough can be scooped into individual cookies 3.4. QUEUES 17

Figure 3.3: Replacing the Put on Sheets input queue from Figure 3.2 with a queue set replaces the serialized Put On Sheets with the combined parallelizable Scoop & Lay Down.

in parallel, but all cookies must route through a single baker to be put onto cookie sheets without conflicts or collisions. The same phenomenon happens in many parallel applications. For example, renderers often shade pixels independently before updating a shared frame buffer. On the one hand, this serialization often becomes a bottleneck, but on the other, introducing fine grained locking of cookie sheet or frame buffer locations has many unpleasant effects: managing explicit locking is a burden on application developers, suffers from contention, and can be subtle to keep correct. Instead, performant parallel applications often subdivide the shared resource into disjoint regions that can each be updated independently.

Figure 3.3 displays queue sets, GRAMPS's construct for applying this technique. A queue set functions like N 'subqueues' bundled together as a single logical queue. Different subqueues can be processed in parallel, but GRAMPS ensures that for each subqueue at most one packet is in flight at a time. In the updated example, each subqueue corresponds to a distinct cookie sheet (or portion of a cookie sheet).

An application can use a queue set statically or dynamically. When used statically, the graph specifies the number of subqueues and the stages reference them with dense indices. Dynamically, producing output to a non-existent subqueue creates it and subqueues are identifies with arbitrary keys that GRAMPS transparently internally maps onto dense indices (or some other suitable data structure).

#### 3.5 Stages

GRAMPS stages correspond to nodes in the execution graph. The fundamental reason to partition computation into stages is to increase performance. Stages operate asynchronously and therefore expose inter-stage parallelism. More importantly, stages encapsulate phases of computation and indicate computations that exhibit similar execution or data access characteristics (typically SIMD processing or memory locality). Grouping these computations together yields opportunities for efficient processing. Additionally, some computations are data-parallel and separating them as distinct stages exposes intra-stage parallelism that GRAMPS can capture with automatic instancing. GRAMPS stages are useful when the benefits of coherent execution and/or greater parallelism outweigh the costs of enqueuing and dequeuing the data.

GRAMPS supports three types of stages that correspond to distinct sets of computational characteristics. A stage's type serves as a hint facilitating work assignment, resource allocation, and computation scheduling. We strove for a minimal number of simple abstractions that still captured the key execution models for mapping well to many-core platforms. In addition to a general purpose Thread stage, we included two others: stages implemented as fixed-function/dedicated hardware processing and data-parallel Streaming/GPGPU-style Shader stages.

A GRAMPS stage definition consists of:

- Type: Either Thread, Fixed-Function, or Shader.

- Program: Either program code for a Thread/Shader or configuration parameters for a fixed-function unit.

- Buffers: Random-access, fixed-size data bindings.

- Queues: Input, Output, In-Place, and "Push"/"Coalescing" queue bindings.

We expect GRAMPS programs to run on platforms with significantly larger numbers of processing resources than stages. Thus, when possible, GRAMPS will execute multiple copies of a stage's program in parallel (each operating on distinct input 3.5. STAGES 19

packets). We refer to each executing copy of a stage as an *instance* while stages that require serial processing (e.g. initialization) execute as *singletons*. Different graphs allow different amounts of instancing. Recall that in Figure 3.2, Scoop Cookies can be freely instanced (but stuck serializing afterwards) whereas in Figure 3.3 the combined Scoop & Lay Down can be instanced only as much as separate subqueues have input (i.e., separate cookie sheets are available).

#### 3.5.1 Thread Stages

Thread stages are best described as traditional CPU-style threads. They are designed for task-parallel, serial, and other regions of an application best suited to large per-element working sets or operations dependent on multiple packets at once (e.g., repacking or re-sorting of data). They are expected typically to fill one of two roles: repacking data between Shader stages, or processing bulk chunks of data where sharing/reuse or cross-communication make data-parallel Shaders inefficient. Importantly, since Thread stages may be stateful—i.e., may retain state internally as they process packets—they usually must be manually parallelized/instanced by the application rather than automatically by GRAMPS. There is one situation in which GRAMPS can instance a Thread stage: if its sole input is a queue set and all of the stage's processing is per-subqueue, then the application can flag the stage and GRAMPS will instantiate one copy for each input subqueue.

Thread stage instances manipulate queues via two GRAMPS intrinsics—reserve, and commit—which operate in-place. Each takes four arguments: the queue, the number of packets, optional flags, and an optional subqueue identifier (either a dense index or a sparse key). reserve returns the caller a "window" that is a reference to one or more contiguous packets. GRAMPS guarantees the caller exclusive access to this region of the queue until it receives a corresponding commit notification. An input queue commit indicates that packet(s) have been consumed and can be reclaimed. Output queue commit operations indicate the packet(s) are now available for downstream stages.

reserve is a potentially blocking operation: an instance will be suspended on an

input reservation if there is no data ready or an output reservation if the queue is currently at its specified capacity. Both reserve and commit are potential preemption points where a scheduler can choose to suspend an instance if a higher priority instance is runnable.

The queue reserve-commit protocol allows stages to perform in-place operations on queue data and allows GRAMPS to manage queue access and underlying storage. Queue windows permit various strategies for queue implementation and add a degree of indirection that enables customized implementations for systems with distributed address spaces, explicit prefetch, or local store capabilities.

#### 3.5.2 Fixed-Function Stages

GRAMPS allows stages to be implemented by fixed-function or specialized hardware units. GRAMPS effectively treats them as Thread stages with peculiar internals: they inter-operate with the rest of GRAMPS via queue reservations and commitments and cannot be instanced. Applications configure these units via GRAMPS by providing hardware-specific configuration information at the time of stage specification.

#### 3.5.3 Shader Stages

Shader stages define short-lived, run-to-completion computations applied independently to every input packet, akin to traditional GPGPU shaders/kernels. They are designed as an efficient mechanism for running data-parallel regions of an application. GRAMPS leverages these properties in two ways: *automatic instancing* and *automatic queue management*. Since Shaders are stateless across packets, GRAMPS can freely create up to as many concurrent instances as there are available packets to ensure large amounts of parallelism.

Additionally, GRAMPS manages queue inputs and outputs for Shader instances automatically, which simplifies Shader programs and allows the scheduler to guarantee they can run to completion without blocking. As input packets arrive in a queue, GRAMPS internally makes corresponding output packet reservations. Once the paired reservations are obtained, GRAMPS runs the packet's worth of Shader

instances. Each instance receives a reference to the shared packet header and to one element in each of the pre-reserved input and output packets (recall that Shader stages use Collection packets, as described in Section 3.4.1). When all of the instances have completed, GRAMPS internally commits the inputs and outputs. With ordered queues, pre-reserving Shader packets also lets GRAMPS ensure that the commit order of output packets corresponds exactly to the order of inputs, and preserve order across stages. Input and output pre-reservation reflects GRAMPS Shaders' GPGPU antecedents, but, like allowing cycles in execution graphs, GRAMPS Shaders have an additional optional operation, push, that significantly extends their flexibility. push dynamically inserts elements into unordered output queues, thus allowing conditional output. Note that unlike reserve and commit, and in sync with the data-parallel nature of Shader stages, push sends individual elements which GRAMPS accumulates into Collection packets. It coalesces as full a packet as possible, sets the element count in the header, and enqueues the packet for downstream consumption.

Push-style coalescing applied to an input queue allows a Shader stage to perform reductions. In this mode, GRAMPS merges elements from partially full input packets to provide the consuming instance with as full a packet as possible. In turn, the consumer compacts/combines all of the elements in the packet to a single result. An application graph can route this once-filtered data downstream or it can bind the input queue "in-place". With an "in-place" binding, the Shader performs a full parallel reduction: compacted output packets are themselves recoalesced into full packets and recirculated down to a single, final result, which GRAMPS propagates downstream as if push'ed.

#### 3.6 Common Design Idioms

In our experience building GRAMPS applications, a few application graph constructs emerged as common building blocks and important cases to consider when tuning a GRAMPS implementation:

• Task generator → Shader consumer: A singleton stage subdivides an input range or read-only buffer into (offset, length) pairs to be processed by a Shader.

Important traits are distributing consumer work to idle processors before preempting the singleton producer and a very simple producer that outputs packets rapidly.

- Shader producer → Shader consumer: The canonical GRAMPS pipeline example: a work-rich instanced producer feeding a freely instanced consumer. The important trait is balancing the resources assigned to each stage. Aggressively preempting producer instances with consumers keeps the queue footprint small, but frequently runs out work and must switch back to producers. Too many context switches, especially rapid ping-ponging, can be expensive.

- Queues as barriers: While GRAMPS applications tend to exhibit producer-consumer parallelism between stages, sometimes an application needs to block one stage until its upstream is entirely done. It does this by issuing an unsatisfiable reserve, generally for -1 packets. This leaves the stage unrunnable until all producers on that queue have completed, at which point GRAMPS returns a short reservation. The important trait is obvious: the blocked stage will not run until all of its input is available. This can influence, for example, decisions on when to wait to coalesce a more full packet versus flush it or when to even check if a stage can be scheduled.

# Chapter 4

# Future Rendering Architectures

This chapter presents a case study of GRAMPS as a programming model for future graphics architectures. We examine a rasterizing and a ray-tracing renderer as well as a hybrid of the two on two simulated platforms: one more heterogeneous and GPU-like and the other more CPU-like. Most of the content of this chapter was published separately in Transactions on Graphics, January 2009 [41].

### 4.1 Introduction

Rendering is the first application domain where we examine GRAMPS. Not only was GRAMPS highly influenced by the graphic pipeline, but rendering is a critical 'table-stakes' area for parallelism, especially heterogeneous and producer-consumer parallelism: the past decade-plus has seen the rise of commodity GPUs with enormous computational power and the ability to render complex, high-resolution scenes in real time using Z-buffer rasterization. At the same time, the real-time photorealistic rendering problem is not solved, and there remains interest in exploring advanced rendering algorithms such as ray tracing, REYES, and combinations of these with the traditional graphics pipeline. Implementing them in the confines of current GPU programming models is awkward and nonperformant (e.g., [20, 46]), however, but GRAMPS potentially fits well.

While the earliest GPUs were simple, application-configurable engines, the history

of high-performance graphics over the past three decades has been the co-evolution of a pipeline abstraction (the traditional graphics pipeline) and the corresponding driver/hardware devices (GPUs). In the recent past, the shading stages of the pipeline became software programmable. Prior to the transition, developers controlled shading by toggling and configuring an assortment of fixed options and parameters, but the widespread innovation in shading techniques led to an increasingly complex matrix of choices. In order to accommodate the trend towards more general shading, researchers and then graphics vendors added programmable shading to the graphics pipeline.

We see an analogy between the evolution from fixed to programmable shading and the current changes for enabling and configuring pipeline stages. After remaining static for a long time, there are a variety of new pipeline topologies available and under exploration. Direct3D 10 added new geometry and stream-output stages [5]. The Xbox 360 added a new stage for tessellation (also included in the latest iterations of Direct3D and in OpenGL via extensions). We believe that future rendering techniques and increasing non-graphical usage will motivate more new pipeline stages and configuration options. As was true with pre-programmable shading, these new abilities are currently all delivered as predefined stage and pipeline options to be toggled and combined. Looking forward, we propose to instead expose the hardware capabilities via GRAMPS and programmatically construct graphics pipelines as GRAMPS applications.

This is not an (unthinkably) radical change. In fact, it formalizes and exposes the key elements of current GPU hardware: FIFOs and work-buffers for flow control and accumulating work, shader cores for data-parallel processing, and custom fixed-function units for other stages, such as rasterization. Also, as suggested above, it mirrors the multi-configuration to programmable transition in shading now applied to the pipeline topology itself. Finally, the notion of 'GPU' itself is changing. At the extreme is Intel's Larrabee [40], an entirely alternate architecture, but even recent generations of conventional GPUs are being described and designed as more general throughput-oriented architectures.

In this chapter, we examine how GRAMPS holds up as a programming model for rendering on future graphics hardware. Specifically, we survey current graphics architectures and programming models and then assess GRAMPS in terms of the design goals from Chapter 1:

- Broad application scope: An OpenGL/Direct3D-like rasterization pipeline, a ray tracing graph, and an extension for the rasterization pipeline to incorporate ray traced effects.

- Multi-platform applicability: GRAMPS runtimes for two simulated architectures: a more general CPU-like system and a more custom GPU-like one.

- **Performance**: Scheduling logic for the two runtimes that demonstrate high scale-out utilization with good queue footprint management.

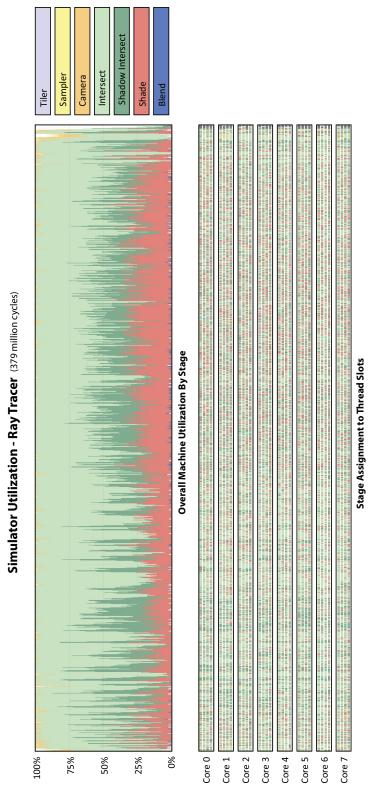

- **Tunability**: Grampsviz, an application for visualizing the execution of our renderers and descriptions of some application graph improvements that had major effects.

## 4.2 Background and Related Work

#### 4.2.1 GPUs

As mentioned above, modern GPUs have become very sophisticated high-performance platforms for real-time graphics. Two widely available examples are NVIDIA's 400-Series [32] and AMD's HD 5000-Series [2], both built around a pool of highly multithreaded programmable cores tuned to sustain multiple teraflops of performance when performing shading computations. They deliver additional computing capabilities via fixed-function units that perform tasks such as rasterization, texture filtering, and frame-buffer blending. While the programmable cores are exposed for general purpose workloads, much of this non-programmable hardware is central to how GPUs schedule graphics and implement the graphics pipeline so efficiently. As a result, GPUs constitute a heavily-tuned platform for rasterization-based z-buffer rendering but offer only limited benefits for alternative graphics algorithms.

Figure 4.1: Our Direct3D-based pipeline including optional extension.

### 4.2.2 Graphics on Stream Processors

Two different prior efforts explored rendering with stream processors/streaming languages: one on Imagine and one on Raw [34, 10]. Both formulated OpenGL-like pipelines as stream applications much like a GRAMPS application graph. Unlike GRAMPS, however, both suffered from needing to constrain (fake) the dynamic irregularity of rendering in predictable terms for their static scheduling.

Both systems redefined and recompiled their pipelines per scene and per frame they rendered. Not only that, as part of tuning and scheduling each scene-specific pipeline they needed to pre-render each frame once to gather statistics first. In the six-plus years since the streaming pipelines were first published, this irregularity and scene-dependent variation has become even more prominent: branching in shaders is routine, as is composing final frames from large numbers of off-screen rendering passes.

Around the same time, Purcell demonstrated a somewhat reverse accomplishment: using the programmable elements of a GPU as a stream processor and performing ray tracing [36]. Stuck inside the Breadth-First-like environment of the graphics pipeline's shading stages, this system and its successors always struggled with load-balancing [14, 20].

27

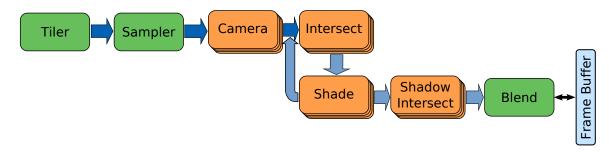

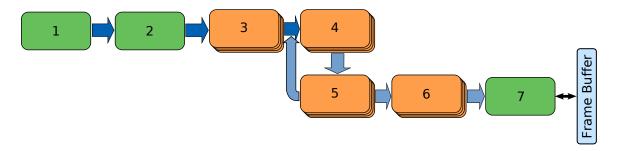

Figure 4.2: Our ray tracing application graph. Note that the queue from Shade back to Intersect (for secondary rays) makes the graph cyclic.

## 4.3 Application Scope

In this section we describe three example rendering systems framed in terms of GRAMPS: a simplified Direct3D pipeline, a packet-based ray tracer, and a hybrid that augments the simplified Direct3D pipeline with additional stages used for ray tracing.

#### 4.3.1 Direct3D

The GRAMPS graph corresponding to our sort-last formulation of a simplified Direct3D pipeline is shown in Figure 4.1. A major challenge of a Direct3D implementation is exposing high levels of parallelism while preserving Direct3D fragment ordering semantics.

The pipeline's front-end consists of several groups of Input Assembly (IA) and Vertex Shading (VS) stages that operate in parallel on disjoint regions of the input vertex set. Currently, we manually create these groups—built-in instancing of subgraphs is a potentially useful future addition to GRAMPS. Each IA/VS group produces an ordered stream of post transform primitives. Each input is assigned a sequence number so that these streams can be collected and totally-ordered by a singleton Reorder (RO) stage before being delivered to the fixed-function rasterizer (Rast).

The pipeline back-end starts with a Pixel Shader (PS) stage that processes fragments. After shading, fragment packets are routed to the appropriate subqueue in the output queue set based on their screen space position, much like described in Section 3.4.2. The queue set lets GRAMPS instance the Output Merger while still guaranteeing that fragments are blended into the frame buffer atomically and in the correct order. Note that Rast facilitates this structure by scanning out packets of fragments that never cross the screen space routing boundaries. Notice that the Direct3D graph contains no stages that correspond to fixed-function texture filtering. While a GRAMPS implementation is free to provide dedicated texturing support (as modern GPUs do through special instructions), special-purpose operations that occur within a stage are considered part of its internal operation, not part of the GRAMPS programming abstraction or any GRAMPS graph.

#### 4.3.2 Ray Tracer

Our implementation of a packet-based ray tracer resembles Purcell's streaming implementation [36] and maps natural components of ray tracing to GRAMPS stages (Figure 4.2). With the exception of Tiler, Sampler, and Blend, whose performance needs are satisfied by singleton Thread stages, all graph stages are instanced Shader stages. All queues in the packet tracer graph are unordered.

A ray tracer performs two computationally expensive operations: ray-scene intersection and surface hit point shading. Considered separately, each of these operations is amenable to wide SIMD processing and exhibits favorable memory access characteristics. Because recursive rays are conditionally traced, SIMD utilization can drop severely if shading directly invokes intersection [6].

Our implementation decouples these operations by making Intersect, Shadow Intersect, and Shade separate graph stages. Thus, each of the three operations executes efficiently on batches of inputs from their respective queues. To produce these batches of work, the ray tracer leverages the GRAMPS queue push operation. When shading yields too few secondary rays to form a complete packet, execution of Intersect (or Shadow Intersect) is delayed until more work is available. Similarly, if too few rays from Intersect need shading, they won't be shaded until a sufficiently large batch is available. This strategy could be extended further using more complex GRAMPS

graphs. For example, separating Intersect into a full subgraph could allow for rays to be binned at individual BVH nodes during traversal.

Lastly, the ability to cast ray tracing as a graph with loops, rather than a feedforward pipeline allows for an easy implementation of both max-depth ray termination and also ray tree attenuation termination by tracking depth/attenuation with each ray [17]. While reflections to a fixed maximal depth could also be modeled with a statically unrolled pipeline, this is an awkward implementation strategy and does not permit ray tree attenuation.

#### 4.3.3 Extended Direct3D

By constructing execution graphs that are decoupled from hardware, GRAMPS creates an opportunity for specialized pipelines. Our third renderer extends the Direct3D pipeline to form a new graph that adds ray-traced effects (Figure 4.1, including the shaded portion). We insert two additional stages, Trace and PS2, between PS and OM and allow Extended Direct3D Pixel Shaders to push rays in addition to performing standard local shading. Trace performs packetized ray-scene intersection and pushes the results to a second shading stage (PS2). Like PS, PS2 is permitted to send its shaded output to OM, or generate additional rays for Trace (the Extended Direct3D graph contains a loop). We introduced PS2 as a distinct stage to retain the ability to specialize PS shading computations for the case of high coherence (fragments in a packet from Rast all originate from the same input triangle) and to separate tracing from shading as explained above.

There are two other important characteristics of our Extended Direct3D renderer. Our implementation uses a pre-initialized early-Z buffer from a prior Z-only pass to avoid unnecessary ray-scene queries. In addition, early-Z testing is required to generate correct images because pixel contributions from the PS2 stage can arrive out of triangle draw order (input to PS2 is an unordered push queue).

Note that while this example uses push only for the purposes of building ray and shading packets, other natural uses include handling fragment repacking when coherence patterns change, or as a mechanism for efficiently handling a constrained form of data amplification or compaction.

## 4.4 Multi-platform

#### 4.4.1 Hardware Simulator

We developed a machine simulator to conduct our evaluation of GRAMPS as a programming model for rendering. We chose to use a simulator instead of existing hardware for three reasons: access, flexibility, and instrumentability. Low-level GPU programming access is highly proprietary and minimally documented. Even with willing vendor collaboration, drivers for modern graphics hardware are enormously complex; customizing them to our ends would be very challenging. Additionally, many of the features we wish to explore, for example, push and Thread stages, are simply unavailable in current hardware. Finally, one of the most important aspects of validation and bring-up, at least for a completely new programming model, is the ability to report a wide variety of system properties. With real hardware, it can be invasive and challenging, if not impossible, to measure a consistent snapshot of system-wide state. In simulation, by contrast, it is straightfoward.

Our simulator is single-threaded (though it simulated the execution of many parallel threads). While this makes simulation slower, it enormously simplifies maintaining such things as a shared, global clock and deterministic execution. Essentially, on every simulated clock, the main simulation loop runs the top-level Tier-N scheduler (see below), and steps each core and any fixed function units until the GRAMPS runtime detects application completion or deadlock (in the case of flawed application graphs that contain loops).

The basic execution resource is a simulated, multi-threaded programmmable core, referred to as an XPU. XPUs use a MIPS64 instruction set architecture [27] extended with a custom 16-wide SIMD vector instruction set that includes basic math and gather/scatter load/store operations. They can select and execute one hardware thread per clock. We develop XPU programs using cross-compiling versions of GCC and GNU Binutils that we extended to support our vector instructions. The

31

core simulation supports many parameters, the most important being the number of execution contexts (hardware threads) and the two latency factors.

Latency in XPU cores is modeled very simply. A core has two values—an 'ALU latency' and a 'memory latency'. The ALU latency is the number of cycles a vector instruction takes to retire. It is applied per-hardware thread, on the presumption of pipelining and/or per-thread resources. That is, a four-threaded XPU with a four cycle ALU latency, for example, can complete one vector instruction per cycle if all of its thread slots are active. Memory latency is also a single value. It functions as the overall (hypothetical) memory hierarchy and is applied to all data accesses (instruction accesses are single cycle). These simple latencies are gross approximations, but we believe them sufficient for assessing GRAMPS's high-level plausibility. One natural area of future research, that is already under initial investigation, is enriching instruction issue and the memory hierarchy so that they can mimic the behaviors of a variety of existing CPU and GPU designs.

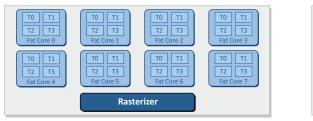

In our experiments, we used two different collections of settings for cores. XPU fat cores are general-purpose cores optimized for throughput. They are in-order, four-threaded processors with both an ALU and memory latency of four cycles. XPU micro cores are intended to resemble GPU shader cores and execute efficiently under the load of many lightweight threads. Each micro core has 24 independent hardware thread execution slots. Thus, with 16-element-at-a-time vector instructions, each micro core is capable of hardware-interleaved execution of 384 Shader instances. However, reflecting their heavy emphasis on longer serial latencies hidden by multi-threading, they are configured with an ALU latency of six cycles and a memory latency of 100 cycles.

To reflect the heterogeneous nature of graphics hardware, and to exercise the Fixed-Function stage support in GRAMPS, we also implemented a simulated hardware rasterizer that can be enabled optionally, as shown by the Direct3D graph (Section 4.3.1). It employs the scan conversion algorithm from [33] and can rasterize an entire triangle in a single simulated clock, to mimic highly optimized custom functional units.

CPU-Like: 8 Fat Cores, Rast

GPU-Like: 1 Fat Core. 4 Micro Cores. Rast. Sched

Figure 4.3: The CPU-like and GPU-like simulator configurations: different mixtures of XPU fat (blue) and micro (orange) cores plus a fixed function rasterizer. Boxes within the cores represent hardware thread slots.

We chose two specific configurations of our simulation environment for the hypothetical graphics architectures in our experiments. They are shown in Figure 4.3. The *GPU-like* configuration contains one fat core, four micro cores with dedicated Shader scheduling/dispatch support (see below), and a fixed-function rasterizer. As the name indicates, It is envisioned as an evolution of current GPUs. The *CPU-like* configuration consists of the rasterizer plus eight fat cores, mimicking a more general purpose many-core implementation. This choice of machine configurations allows us to explore two GRAMPS scheduler implementations employing different levels of hardware support.

#### 4.4.2 GRAMPS Runtimes

We built implementations of GRAMPS for the two configurations directly into the simulator (as opposed to running them as simulated code). In addition to implementing the programming model, they function as mini-operating systems: application code calls GRAMPS via the MIPS syscall instruction and GRAMPS interacts directly with the XPU logic to, for example, launch and context-switch hardware threads. Their primary nontrivial run-time components are their queue implementation, dispatch of Shader instances, and scheduling. The first two are discussed below and scheduling is discussed in detail as part of performance (Section 4.5.1).

Both simulated GRAMPS runtimes share the same queue implementation: one fixed-sized circular buffer per application queue, sized to the capacity specified in

33

the application graph. Ordered queues use the buffer as a rolling FIFO: there are head and tail pointers, each with separate 'reserve' and 'commit' marks. These are updated on reserve and commit, respectively, and wrap around when they reach the end of the buffer. The region between the head 'reserve' and 'commit' reflects pending output reservations (packets being produced) and the region between the tails marks reflects pending input reservations (packets being consumed). The entries between the tail 'reserve' and head 'commit' are packets available for consumption and the space between the head 'reserve' and tail 'commit' is empty. Unordered queues are simpler. They have two bitvectors: one indicating buffer entries that contain packets available for input and one tracking entries with packets available for output.